## Micro 8 bits : l'ATMEGA 8

David Delfieu

Département Génie Electrique 3<sup>ième</sup> année

# Acronyms

- ADCH*** Analog to Digital Converter High. 20

- ADCL*** Analog to Digital Converter Low. 20

- GICR*** General Interrupt Control Register. 12, 13

- MCUCR*** Management Control Unit Control Register. 9, 12

- MCUCSR*** MCU Control and Status Register. 13

- SPI*** Serial Peripheral Interface. 7

- SRAM*** Static Random Access Memory. 6

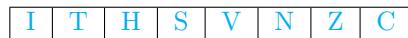

- SREG*** *I T H S V N Z C*. 8

- USART*** Universal Synchronous and Asynchronous Serial Receiver. 7

- ACIC*** Analog Comparator Input Capture Enable. 33

- ACO*** Analog Comparator Output. 32, 33

- COM<sub>1</sub>x<sub>1</sub> : 0*** Compare Output Mode x(A or B) 1:0. 33–35, 37, 38

- ICF<sub>1</sub>*** Input Compare Flag 1. 30, 32

- ICNC<sub>1</sub>*** Input Capture Noise Canceller 1. 33

- OCF<sub>1A</sub>*** Output Compare Flag 1 A. 30, 32

- OCF<sub>1B</sub>*** Output Compare Flag 1 B. 30, 32

- TICIE<sub>1</sub>*** Timer Input Capture Interrupt Enable 1. 32

- TOV<sub>1</sub>*** Timer Overflow 1. 30, 32

- WGM<sub>1</sub>3:0*** Wave Generation Modes 3:0. 32–35

- ACS ACD ACO ACI ACIE ACIC ACIS<sub>1</sub> ACIS<sub>0</sub>***. 33

- ADCSRA ADEN ADSC ADATE ADIF ADIE ADPS<sub>2</sub> ADPS<sub>1</sub> ADPS<sub>0</sub>***. 21

- ADMUX REFS<sub>1</sub> REFS<sub>0</sub> ADLAR MUX<sub>4</sub> MUX<sub>3</sub> MUX<sub>2</sub> MUX<sub>1</sub> MUX<sub>0</sub>***. 21

- ASSR*** Asynchronous Status Register. 47

- ICR<sub>1</sub>*** Input Capture Register. 31–33, 36, 39, 40

- OCR<sub>1A</sub>*** Output Compare Register 1 A. 31, 32, 35, 36, 39, 40

- OCR<sub>1B</sub>*** Output Compare Register 1 B. 31, 32, 35

- OCR<sub>1x</sub>*** Output Compare Register 1 x=A ou B. 36, 37, 40

- OCR<sub>2</sub>*** Output Compare Register 2. 42–48

**OC<sub>1A</sub>** Sortie *MLI* A du timer 1. 35

**OC<sub>1X</sub>** Sorties *MLI* A ou B du timer 1. 38

**SFIOR** *ADTS2 ADTS1 ADTS0 – ACME PUD PSR2 PSR10*. 15, 28

**TCCR<sub>0</sub>** – – – – *CS<sub>02</sub> CS<sub>01</sub> CS<sub>00</sub>*. 27

**TCCR<sub>1A</sub>** *COM1A<sub>1</sub> COM1A<sub>0</sub> COM1B<sub>1</sub> COM1B<sub>0</sub> FOC1<sub>1</sub> FOC1<sub>B</sub> WGM1<sub>1</sub> WGM1<sub>0</sub>*. 31, 32, 38

**TCCR<sub>1B</sub>** *ICN<sub>1</sub> ICES – WGM1<sub>3</sub> WGM1<sub>2</sub> CS1<sub>2</sub> CS1<sub>1</sub> CS1<sub>0</sub>*. 31–33, 39

**TCCR<sub>2</sub>** Timer Counter Control Register 2. 43, 46

**TCNT<sub>0</sub>** Timer Counter Timer 0. 27, 28

**TCNT<sub>1</sub>** Timer Counter Timer 1. 31, 32, 34–37, 39, 40

**TCNT<sub>2</sub>** Timer Counter Timer 2. 42–48

**TIFR** *OCF2 TOV<sub>2</sub> ICF<sub>1</sub> OCF1A OCF1<sub>B</sub> TOV<sub>1</sub> – TOV<sub>0</sub>*. 27, 31, 40, 42

**TIMSK** *OCIE<sub>2</sub> TOIE<sub>2</sub> TICIE<sub>1</sub> OCIE<sub>1A</sub> OCIE<sub>1B</sub> TOIE<sub>1</sub> – TOIE<sub>0</sub>*. 5, 27, 28, 31, 40, 48

**ACSR** Comparateur analogique. 19

**ADCH** Poids fort de la conversion analogique. 4, 22

**ADCL** Poids faible de la conversion analogique. 4, 22

**ADCSRA** Contrôle du convertisseur analogique. 4, 21, 22

**ADMUX** Multiplexeur analogique. 4, 22

**EPPROM** Petite mémoire non volatile qui contient des données dynamiques. Elle a un temps d'accès très lent, autour de 5 millisecondes pour un *ATMEGA8*. 6, 8

**FLASH** Mémoire non volatile qui contient le programme et les données statiques. Par rapport à la *SRAM*, elle a un temps d'accès plus lent ainsi qu'une durée de vie est assez limitée, par contre elle a une consommation faible. 6, 8

**GICR** Gestion des interruptions. 12

**ICP1** Patte du timer 1 sur laquelle on peut réaliser une entrée de capture (*PB<sub>0</sub>*). 33

**MCUCR** Gère notamment les activations des *interruptions* externes. 12

**MLI** Modulation de Largeur d'Impulsions. 7

**OC1A** Patte du timer 1 sur laquelle on peut observer une *MLI* (*PB<sub>1</sub>*). 35

**OC1B** Patte du timer 1 sur laquelle on peut observer une *MLI* (*PB<sub>2</sub>*). 35

**OSCCAL** Calibration et gestion du résonnateur. 10

**PUD** Inhibe les résistances de tirage. 15

**SFIOR** Résistances de tirage et le pré-diviseur des timer 0 et 1. 15, 19

**SRAM** Mémoire volatile qui contient les données dynamiques. Elle est contient notamment tous les registres du **microcontrôleur**. 6, 8

**SREG** Registre qui contrôle les bits d'état du **microcontrôleur** comme la Carry, le bit Zero, le bit Négatif, .... 8

**TCCR0** Pré-diviseur du timer 0. 4, 27

**TCNT0** Registre de comptage du timer 0. 4, 27

# Contents

|                                                                                                                                     |           |

|-------------------------------------------------------------------------------------------------------------------------------------|-----------|

| <b>1 Présentation générale</b>                                                                                                      | <b>4</b>  |

| 1.1 Introduction . . . . .                                                                                                          | 4         |

| 1.1.1 Les différents blocs mémoire de l' <i>ATMEGA</i> <sub>8</sub> . . . . .                                                       | 4         |

| 1.1.2 Fonctionnalités . . . . .                                                                                                     | 5         |

| 1.1.3 Les modes de communication de l' <i>ATMEGA</i> <sub>8</sub> . . . . .                                                         | 5         |

| 1.2 Architecture . . . . .                                                                                                          | 5         |

| 1.2.1 Architecture interne . . . . .                                                                                                | 6         |

| 1.2.2 Registres Systèmes . . . . .                                                                                                  | 7         |

| 1.2.3 Horloges et modes des sommeil de l' <i>ATMEGA</i> <sub>8</sub> . . . . .                                                      | 8         |

| 1.3 Les modes interruptifs de l' <i>ATMEGA</i> <sub>8</sub> . . . . .                                                               | 9         |

| 1.3.1 Les <i>interruptions</i> . . . . .                                                                                            | 10        |

| 1.3.2 Les <i>interruptions</i> externes . . . . .                                                                                   | 10        |

| 1.3.3 Le chien de garde . . . . .                                                                                                   | 11        |

| 1.4 Les Ports . . . . .                                                                                                             | 11        |

| 1.4.1 Paramétrage et usage des <i>PORTS</i> . . . . .                                                                               | 12        |

| 1.4.2 Résistance de tirage : Pull-up resistor . . . . .                                                                             | 13        |

| 1.4.3 Registres de manipulation des ports : <i>DDR</i> <sub>x</sub> , <i>PIN</i> <sub>x</sub> et <i>PORT</i> <sub>x</sub> . . . . . | 13        |

| 1.4.4 Le Port B . . . . .                                                                                                           | 13        |

| 1.4.5 <i>PORTC</i> . . . . .                                                                                                        | 14        |

| 1.4.6 <i>PORTD</i> . . . . .                                                                                                        | 14        |

| 1.4.7 Lecture et écriture sur un port . . . . .                                                                                     | 15        |

| 1.4.8 Lecture d'un Port . . . . .                                                                                                   | 15        |

| 1.4.9 Fonction de manipulation de bits . . . . .                                                                                    | 15        |

| <b>2 Conversion Analogique</b>                                                                                                      | <b>16</b> |

| 2.1 Le Comparateur Analogique . . . . .                                                                                             | 16        |

| 2.1.1 Fonctionnement global . . . . .                                                                                               | 16        |

| 2.1.2 Les registres . . . . .                                                                                                       | 17        |

| 2.2 Le Convertisseur Analogique-Numérique : <i>ADC</i> . . . . .                                                                    | 18        |

| 2.2.1 Fonctionnement et caractéristiques . . . . .                                                                                  | 18        |

| 2.2.2 Les différentes méthodes de programmation d'une conversion . . . . .                                                          | 20        |

| 2.2.3 Les Registres de l' <i>ADC</i> : <i>ADMUX</i> , <i>ADCSRA</i> , <i>ADCH</i> , <i>ADCL</i> . . . . .                           | 20        |

| <b>3 Les Timers</b>                                                                                                                 | <b>24</b> |

| 3.1 Le <i>timer</i> 0 . . . . .                                                                                                     | 24        |

| 3.1.1 Caractéristiques . . . . .                                                                                                    | 24        |

| 3.1.2 Les registres associés au <i>timer</i> 0 : <i>TCCR0</i> , <i>TCNT0</i> . . . . .                                              | 25        |

| 3.1.3 Le prédiviseur . . . . .                                                                                                      | 26        |

| 3.2 Le <i>timer</i> 1 . . . . .                                                                                                     | 28        |

| 3.2.1 Caractéristiques générales . . . . .                                                                                          | 28        |

| 3.2.2 Les 16 modes du <i>timer</i> 1 . . . . .                                                                                      | 32        |

| 3.2.3 Les Modes du générateur de formes . . . . .                                                                                   | 33        |

| 3.2.4 Inventaire des registres utiles au <i>timer</i> 1 . . . . .                                                                   | 36        |

| 3.2.5 Résumé des 16 modes de <i>MLI</i> du <i>timer</i> 1 . . . . .                                                                 | 39        |

| 3.2.6 Exemples d'utilisation du <i>timer</i> 1 . . . . .                                                                            | 39        |

|          |                                                      |           |

|----------|------------------------------------------------------|-----------|

| 3.3      | Le <b>timer</b> 2 . . . . .                          | 40        |

| 3.3.1    | Aperçu du <b>timer</b> 2 . . . . .                   | 40        |

| 3.3.2    | Génération de forme : pulse, <i>PWM</i> , . . . . .  | 41        |

| 3.3.3    | Les modes du <b>timer</b> 2 . . . . .                | 42        |

| 3.3.4    | Les registres utiles au <b>timer</b> 2 . . . . .     | 44        |

| 3.3.5    | Les <i>interruptions</i> du <b>timer</b> 2 . . . . . | 46        |

| 3.3.6    | <b>TIMSK</b> . . . . .                               | 46        |

| 3.3.7    | TIFR . . . . .                                       | 46        |

| <b>4</b> | <b>La programmation</b>                              | <b>48</b> |

| 4.1      | Langage <i>C</i> . . . . .                           | 48        |

| 4.1.1    | Structure d'un programme . . . . .                   | 48        |

| 4.1.2    | Entête . . . . .                                     | 48        |

| 4.1.3    | Main . . . . .                                       | 48        |

| 4.1.4    | Fonctions . . . . .                                  | 49        |

| 4.1.5    | Déclaration de variable globales . . . . .           | 49        |

| 4.1.6    | Fonction de manipulation de bits . . . . .           | 50        |

| 4.1.7    | Mise en oeuvre d'une interruption . . . . .          | 50        |

| 4.2      | Interruptions . . . . .                              | 51        |

# Chapter 1

## Présentation générale

### 1.1 Introduction

Un **microcontrôleur** est un microprocesseur dédié au contrôle, il contient dans un même composant une unité de calcul **CPU**, comme dans un micro-processeur, mais il a, par contre la possibilité d'adresser directement des Ports d'entrées-sorties (impossible pour un microprocesseur). Il a de plus, spécifiquement, des timers, des convertisseurs analogiques, des unités de communication et de la mémoire.

Ce cours présente l'**ATMEGA8**, **microcontrôleur** de la famille **Arduino** ( Microchip anciennement Atmel) sur lequel on développera des programmes en langage **C** dans l'environnement **Arduino**. On n'utilisera pas cependant le langage **Arduino** leur préférant un structure **C** et la manipulation de registres.

#### La famille des **ATMEGA8**

| Modèle           | Flash | EEPROM | RAM  | IO | PWM | Interfaces     | CAN     |

|------------------|-------|--------|------|----|-----|----------------|---------|

| <b>ATMEGA8</b>   | 8K    | 512    | 1024 | 23 | 3   | SPI-USART      | 10 bits |

| <b>ATMEGA16</b>  | 16K   | 512    | 1024 | 32 | 4   | SPI-USART      | 10 bits |

| <b>ATMEGA32</b>  | 32K   | 1k     | 2k   | 32 | 4   | SPI - USART    | 10 bits |

| <b>ATMEGA64</b>  | 64K   | 2k     | 4k   | 53 | 8   | SPI - USART(2) | 10 bits |

| <b>ATMEGA128</b> | 128K  | 4k     | 4k   | 53 | 8   | SPI - USART(2) | 10 bits |

| <b>ATMEGA256</b> | 256K  | 4k     | 8k   | 53 | 16  | SPI - USART(2) | 10 bits |

Dans cette famille, l'**ATMEGA8** et l'**ATMEGA16** sont compatibles broches à broches et il n'y a que très peu de différences au niveau du code. On pourrait sur la carte de **TP** remplacer facilement un **ATMEGA8** par un **ATMEGA16**.

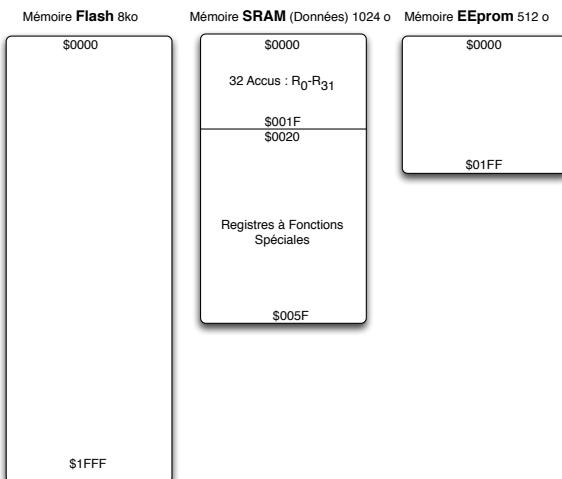

#### 1.1.1 Les différents blocs mémoire de l'**ATMEGA8**

La mémoire de l'**ATMEGA8** est constituée de 1ko de Mémoire vive (SRAM), de 512 octets de EEPROM et de 8ko de mémoire FLASH.

La mémoire de type SRAM contient les registres et la pile système. La mémoire de type Static Random Access Memory (**SRAM**) est un type de mémoire vive “volatile” utilisant des bascules pour mémoriser les données. En l'absence d'alimentation les données sont perdues. Pour placer des variables dans cet espace, on utilisera l'attribut **volatile**. Par exemple : **volatile int i;** Cet attribut assure que la variable sera déclarée dans la SRAM, en dehors de la zone des registres spéciaux. Cela assure à une variable globale de ne pas être perturbée par des modifications de ces registres.

La mémoire FLASH permet 10.000 cycles d'écriture. Elle contient le programme et les données. C'est une mémoire non volatile. Par rapport à la SRAM, elle a un des temps d'accès moins rapide, une durée de vie est assez limitée mais une consommation faible. Elle est même nulle au repos. La FLASH utilise comme cellule de base un transistor **MOS** possédant une grille flottante enfouie au milieu de l'oxyde de grille, entre le canal et la grille. L'information est stockée grâce au piégeage d'électrons dans cette grille flottante. Cette technologie se décline sous deux principales formes : **NOR** et **NAND**, d'après le type de porte logique utilisée pour chaque cellule de stockage. Dans l'**ATMEGA8** on a une FLASH de type **NOR**. Les mémoires de type **NAND** sont plutôt consacrées aux mémoires de masse externes telles que les Cartes **SD**, **disque dur**,...

Les **mémoires** de type EEPROM sont les plus chères. Elle autorisent 100.000 cycles d'écriture. Elles ont un temps d'accès un peu plus long, et donc on y stocke des données qui n'ont pas vocation à être modifiée souvent. Une autre différence avec la FLASH classique est que l'on y écrit octet par octet.

## 1.1.2 Fonctionnalités

Les différentes fonctionnalités sont les **timers**, le convertisseur analogique (**ADC**), les possibilités de communication, les **mémoires** et les **PORTS**d'entrées/sorties. Un **timer** peut définir des bases de temps, faire du comptage d'événements, ou bien générer des MLI ou de gérer un watchdog <sup>1</sup>. L'**ADC** permet de convertir en valeurs numériques codées sur 10 bits des tensions entre 0v et 5v. Les **PORTS** permettent d'adresser et de communiquer avec des composants externes.

## 1.1.3 Les modes de communication de l'ATMEGA<sub>8</sub>

L'ATMEGA<sub>8</sub> dispose de manière interne d'un circuit dénommé Universal Synchronous and Asynchronous Serial Receiver (**USART**). A noter qu'on entend couramment parler d'**UART**, mais qu'Atmel a ajouté ici un *S* pour *Synchronous*. Ce qui veut dire que cette interface peut servir à faire aussi bien de la communication série synchrone ou asynchrone, c'est à dire avec des bits de start et de stop, mais aussi synchrone dans laquelle les bits de données sont envoyés de manière cadencée par un signal de clock, piloté par un maître du protocole de communication. Elle utilise deux fils : un pour l'émission et un pour la réception.

La communication série de type **SPI** est un bus de donnée série synchrone baptisé ainsi par Motorola, et qui opère en Full Duplex. Les circuits communiquent selon un schéma maître-esclaves, où le maître s'occupe totalement de la communication. Plusieurs esclaves peuvent co-exister sur un bus, la sélection du destinataire se fait par une ligne dédiée entre le maître et l'esclave appelée *chip select*.

Le bus Serial Peripheral Interface (**SPI**) contient 4 signaux logiques :

- **SCLK** : Horloge (généré par le maître)

- **MOSI** : Master Output, Slave Input (généré par le maître)

- **MISO** : Master Input, Slave Output (généré par l'esclave)

- **SS** : Slave Select, Actif à l'état bas, (généré par le maître)

La liaison **SPI** est utilisée pour la programmation de l'ATMEGA<sub>8</sub>.

Grâce à une liaison série de l'ATMEGA<sub>8</sub> on peut loader un programme à exécuter dans le **microcontrôleur** Mais on peut aussi communiquer de façon synchrone (**PI**) ou asynchrone (**TWI**) avec des composants externes.

## 1.2 Architecture

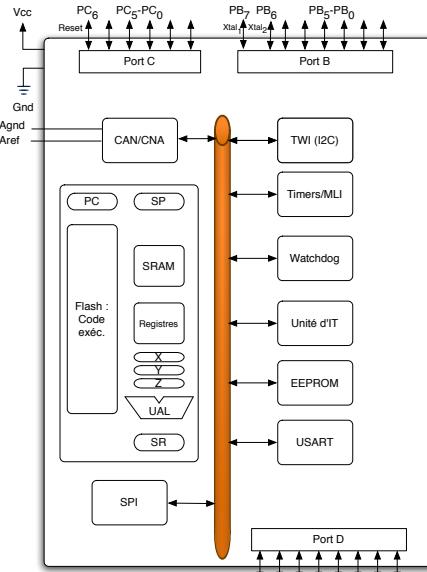

L'architecture du **microcontrôleur** est illustrée dans la figure suivante :

<sup>1</sup>Système de surveillance de bon déroulement de programme : Un watchdog est capable de détecter si un programme sort de sa boucle infinie déclenchant alors un reset qui remettra le programme dans sa boucle

### 1.2.1 Architecture interne

Comme on l'a vu, il y a trois sortes de mémoires :

La mémoire FLASH : stocke le programme (10.000 cycles)

La mémoire SRAM (mémoire donnée) :

les 32 accus ;

les registres à fonctions spéciales ;

la pile.

La mémoire EEPROM : on y place des données stratégiques (100 000 cycles)

| Registres | Adresse | Fonction       |

|-----------|---------|----------------|

| $R_0$     | \$00    | Accumulateur   |

| $R_1$     | \$01    | Accumulateur   |

| ...       | ...     | accu           |

| $R_{25}$  | \$19    | Accumulateur   |

| $R_{26}$  | \$1A    | X poids faible |

| $R_{27}$  | \$1B    | X poids Fort   |

| $R_{28}$  | \$1C    | Y poids faible |

| $R_{29}$  | \$1D    | Y poids Fort   |

| $R_{30}$  | \$1E    | Z poids faible |

| $R_{31}$  | \$1F    | Z poids Fort   |

Les 32 registres internes sont :

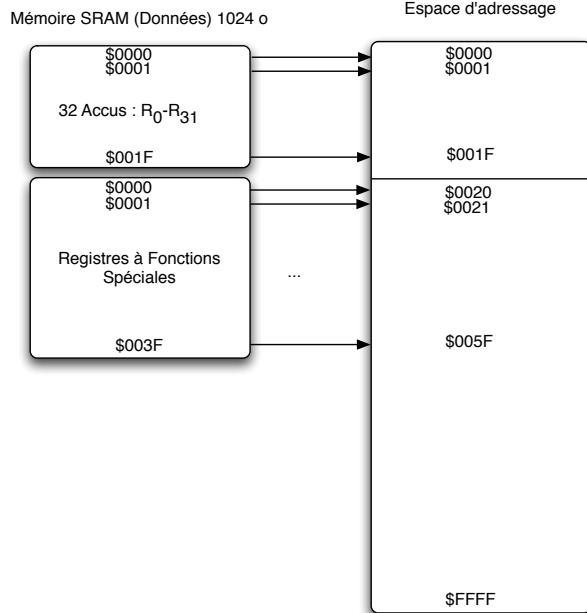

Un mapping signifie une projection d'un plan mémoire sur l'espace d'adressage. Dans l'*ATMEGA8*, certains plans partagent un même espace d'adressage. On distinguera alors l'accès aux variables partageant ce même espace par l'utilisation de modes d'adressage spécifiques.

### 1.2.2 Registres Systèmes

Ces registres agissent sur le contrôle ou indiquent l'état du processeur.

**Registre *SREG*:** SREG est un registre crucial dans ce micro-contrôleur. C'est lui qui surveille en permanence le microcontrôleur et positionne ces bits en fonction de la dernière opération arithmétique ou logique. Par exemple si la dernière opération donne un résultat négatif le bit *N* de *SR* passe à un.

- *C*: Carry

- *Z* : Zero

- *N* : Negative

- *V* : oVerflow =  $C_8 \oplus C_7$

- *S* :  $V \oplus N$

- *H* : Half carry

- *T* : copy sTorage : bit tampon pour manipuler un bit

- *I* : autorisation générale des *interruptions* : *sei()* – *cli()*

**Registre de pile *SP*** Ce registre permet les appels de sous-programmes et le passage de paramètres et la sauvegarde de l'état courant d'un programme. En assembleur, une pile se manipule par les instructions :

PUSH : Empile une donnée, décrémente *SP*

POP : Dépile une donnée, incrémente *SP*

Comme les piles Motorola, la pile de l'Atmel, fonctionne par adresses décroissantes. Par défaut *SP* contient : 0x60 et il faudra changer cette valeur par la valeur : 0x1FF

### 1.2.3 Horloges et modes des sommeil de l'ATMEGA8

**Les modes de sommeil :** Registre *MCUCR* Ce registre définit les différents modes de sommeil dans lequel le micro peut être plongé :

|    |     |     |     |       |       |       |       |

|----|-----|-----|-----|-------|-------|-------|-------|

| SE | SM2 | SM1 | SM0 | ISC11 | ISC10 | ISC01 | ISC00 |

|----|-----|-----|-----|-------|-------|-------|-------|

Les bits de configuration des modes de sommeil *SM<sub>i</sub>*:

| SM2 | SM1 | SM0 | Mode de Sommeil                      |

|-----|-----|-----|--------------------------------------|

| 0   | 0   | 0   | Mode attente                         |

| 0   | 0   | 1   | Mode réduction de bruit pour l'ADC   |

| 0   | 1   | 0   | Mode sommeil (Power down)            |

| 0   | 1   | 1   | Mode économie d'énergie (Power save) |

| 1   | 0   | 0   | Réservé                              |

| 1   | 0   | 1   | Réservé                              |

| 1   | 1   | 0   | Non utilisé                          |

| 1   | 1   | 1   | En pause                             |

|            | Domaines d'horloges actives |     |     |    |     | Oscillateurs |     | Sources de reveil |     |     |    |     |     |     |

|------------|-----------------------------|-----|-----|----|-----|--------------|-----|-------------------|-----|-----|----|-----|-----|-----|

|            | Sommeil                     | CPU | FLA | IO | ADC | ASY          | QTZ | TIM               | INT | TWI | T2 | EEP | ADC | IOs |

| Power Down |                             |     |     |    |     |              |     |                   | X   | X   |    |     |     |     |

| En pause   |                             |     |     |    |     |              | X   |                   | X   | X   |    |     |     |     |

| Power Save |                             |     |     |    |     | X            |     | X                 | X   | X   | X  |     |     |     |

| Réd. bruit |                             |     |     |    | X   | X            | X   | X                 | X   | X   | X  | X   | X   |     |

| Attente    |                             |     | X   | X  | X   | X            | X   | X                 | X   | X   | X  | X   | X   | X   |

### Calibration et le contrôle de l'horloge OSCCAL

|      |      |      |      |      |      |      |      |

|------|------|------|------|------|------|------|------|

| CAL7 | CAL6 | CAL5 | CAL4 | CAL3 | CAL2 | CAL1 | CAL0 |

|------|------|------|------|------|------|------|------|

Valeur de calibrage de l'oscillateur pour la programmation de la mémoire flash ou de l'eprom.

Suivant la configuration de certains bits, on peut utiliser les résonateurs suivants :

- Résonateur externe type céramique ou crystal

- Cristal externe basse fréquence

- Oscillateur externe ou interne de type RC

- Oscillateur calibré interne de type RC

- Horloge externe de type quelconque

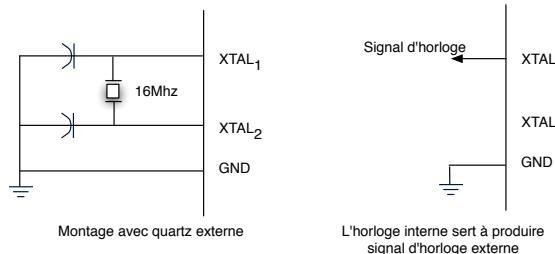

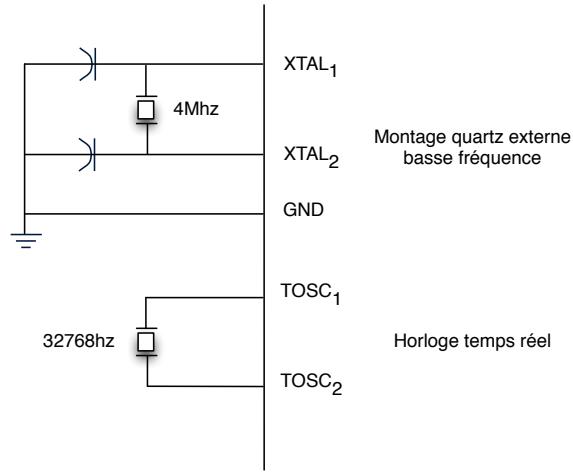

La figure suivante (fig. 1.2.3) présente un montage en quartz externe basse fréquence :

Figure 1.1: Quartz haute fréquence

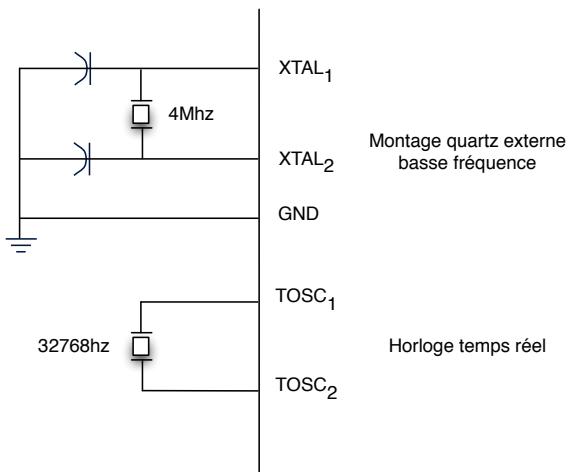

On parle d'horloge temps réel lorsqu'elle permet de générer des diviseurs ou des multiples entier de la seconde. La figure suivante (fig. 1.2.3) combine le positionnement d'un quartz externe et d'une horloge temps réel :

Figure 1.2: Quartz basse fréquence

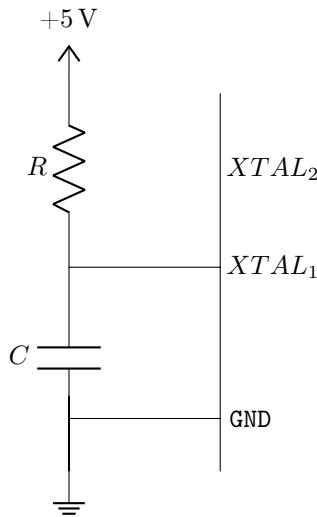

La figure suivante (fig. 1.2.3) présente un montage en résonateur externe :

Figure 1.3: Résonateur externe

Tableau récapitulatif de tous les registres systèmes :

| Adresse     | Nom           | Bit 7                                               | Bit 6  | Bit 5 | Bit 4   | Bit 3  | Bit 2 | Bit 1 | Bit 0 |

|-------------|---------------|-----------------------------------------------------|--------|-------|---------|--------|-------|-------|-------|

| 0x31 (0x51) | <i>OSCCAL</i> | Registre de calibration et de contrôle de l'horloge |        |       |         |        |       |       |       |

| 0x34 (0x54) | <i>MCUCSR</i> | -                                                   | -      | -     | -       | WDRF   | BORF  | EXTRF | PORF  |

| 0x35 (0x55) | <i>MCUCR</i>  | SE                                                  | SM2    | SM1   | SM0     | ISC11  | ISC10 | ISC01 | ISC00 |

| 0x37 (0x57) | <i>SPMCR</i>  | SPMIE                                               | RWWBSB | -     | RWWBSRE | BLBSET | PGWRT | PGERS | SPMEN |

| 0x3D (0x5D) | <i>SPL</i>    | SP7                                                 | SP6    | SP5   | SP4     | SP3    | SP2   | SP1   | SP0   |

| 0x3E (0x5E) | <i>SPH</i>    | -                                                   | -      | -     | -       | -      | SP10  | SP9   | SP8   |

| 0x3F (0x5F) | <i>SREG</i>   | I                                                   | T      | H     | S       | V      | N     | Z     | C     |

### 1.3 Les modes interruptifs de l'ATMEGA8

Un microcontrôleur fonctionne de façon normale en exécutant la boucle infinie de son programme principal. Il peut aussi être interrompu par un événement unique ou récurrent pour exécuter un sous-programme associé. Il y a deux sortes

d'interruptions : Les *interruptions* internes liées aux **timers**, à l'**ADC**, ... ou des *interruptions* externes.

### 1.3.1 Les *interruptions*

Une *interruption* externe correspond à la prise en compte d'un évènement dont l'occurrence possiblement aléatoire. Lors de la survenue de cet évènement ou exécute un sous-programme associé. Ces événements peuvent être par exemple :

- La fin d'un délai,

- La fin de conversion,

- Le compteur d'un **timer** atteint un seuil

- Un front sur une patte du **microcontrôleur**

Un front sur une patte peut correspondre au niveau applicatif à :

- Un arrêt d'urgence provoqué par l'appui d'un bouton ad. hoc.

- Capteur de choc ou de contact

- Dépassement de seuil sur un capteur de température, ...

D'un point de vue programmation, il serait donc peu intéressant d'utiliser des boucles d'attentes de cette alarme. Son traitement est donc réalisé en associant un sous-programme à un évènement. On associe un évènement à un sous-programme par la primitive ISR.

### 1.3.2 Les *interruptions* externes

L'**ATMEGA8** offre deux *interruptions* externes sur deux pattes :  $INT_0(PD_2)$  et  $INT_1(PD_3)$ . Les événements qui peuvent se produire sur ce type de patte sont soit un front montant, soit un front descendant, soit un changement de niveau.

Associer un évènement à un sous-programme se fait en utilisant l'instruction ISR auquel on passe un nom d'évènement :  $ISR(Nom\_evenement)$  et du code entre accolades. L'ensemble des évènements est données dans les tables de la section 4.2. Exemple :

```

ISR(INT0_vect){

PORTD ^= 0xF0; // code associe a l'interruption

}

int main(){

DDRD=0xF0;

GICR |= 1<<INT0;

MCUCR |= 1<<ISC01; // Front descendant

sei();

while(1){}

}

```

Si l'évènement  $INT_0$  (front sur la patte  $PD_2$ ) se produit, quel que soit le comportement de la boucle infinie du programme principal (*main*), le travail est interrompu pour exécuter le sous-programme associé qui est défini entre les deux accolades du bloc *ISR*. A la fin du sous-programme d'*interruption* on revient là où l'on a été interrompu. La mise en oeuvre d'une *interruption* externe se fait grâce aux registres *GICR* et *MCUCR* :

- GICR :

|      |      |   |   |   |   |       |      |

|------|------|---|---|---|---|-------|------|

| INT1 | INT0 | - | - | - | - | IVSEL | IVCE |

|------|------|---|---|---|---|-------|------|

- $INT_0$  : à un, autorise une interruption externe sur la patte  $PD_2$

- $INT_1$  : à un, autorise une interruption externe sur la patte  $PD_3$

- MCUCR :

|    |     |     |     |       |       |       |       |

|----|-----|-----|-----|-------|-------|-------|-------|

| SE | SM2 | SM1 | SM0 | ISC11 | ISC10 | ISC01 | ISC00 |

|----|-----|-----|-----|-------|-------|-------|-------|

Considérons une *interruption* externe  $INT_0$ . Les bits  $ISC_{01}, ISC_{00}$  correspondent alors à la patte  $PD_2$  et le niveau d'activité est défini par le tableau suivant :

- 00 : niveau bas

- 01 : front montant ou descendant

- 10 : front descendant

- 11 : front montant

#### Autres bits du registre *GICR*

- *IVSEL* : Interrupt Vector Select

Quand le bit *IVSEL* est mis à zéro, les vecteurs d'interruption sont placés au début de la la mémoire flash. Quand ce bit est mis à un, les vecteurs d'interruption sont déplacés au début de la zone du boot loader de la mémoire flash. L'adresse de cette zone est modifiable par les bits "fusibles" *BOOTSZ*.

- *IVSEL* : à un, autorise le changement du bit *IVSEL*

Parmi les différents modes de fonctionnement d'un micro-contrôleur on peut citer le fonctionnement "chien de garde".

#### 1.3.3 Le chien de garde

Un chien de garde permet de relancer/réinitialiser le programme. En effet lors d'une perturbation électromagnétique, par exemple, le déroulement du programme peut être altéré : Le compteur programme peut alors essayer d'exécuter du code dans une zone mémoire non prévue. Un chien de garde, par exemple, armé toutes les 500 millisecondes, peut alors resetter le programme et le remettre dans un déroulement normal.

#### Registre *MCUCSR*

|   |   |   |   |             |             |              |             |

|---|---|---|---|-------------|-------------|--------------|-------------|

| - | - | - | - | <b>WDRF</b> | <b>BORF</b> | <b>EXTRF</b> | <b>PORF</b> |

|---|---|---|---|-------------|-------------|--------------|-------------|

- **WDRF** Watchdog Reset Flag: mis à un pour activer le watchdog, raz par un reset ou par une écriture d'un 0

- **BORF** : mis à un lors d'une panne d'électricité partielle, raz par reset ou écriture de 0.

- **EXTR** et **PORF** : Détermine la source d'un reset.

## 1.4 Les Ports

Dans un système à base de **microcontrôleur** on appelle "**PORT** d'entrées-sorties", des ensembles de 8 connections entre le **microcontrôleur** et l'exterieur. Par ces ports, le système peut réagir à des modifications de son environnement, voire le contrôler. Elles sont parfois désignées par l'acronyme *I/O*, issu de l'anglais *Input/Output* ou encore *E/S* pour *Entrées/Sorties*. Ces **PORTS** sont programmables en entrée ou en sortie.

Des buffers sont associés aux **PORTS**, ils ont la capacité d'être à la fois source ou drain de courant ou en haute impédance. Une ligne d'un **port** d'entrées est essentiellement composé d'un tampon à trois états. Ceux-ci se comportent comme des interrupteurs électroniques qui font apparaître, au moment voulu, soit deux niveaux logiques : zéro ou un et un état de haute impédance. Les niveaux logiques sont mémorisés dans un registre du processeur.

| Nom                | B7     | B6     | B5     | B4     | B3     | B2     | B1     | B0     |

|--------------------|--------|--------|--------|--------|--------|--------|--------|--------|

| PORT D             |        |        |        |        |        |        |        |        |

| PIND               | PIND7  | PIND6  | PIND5  | PIND4  | PIND3  | PIND2  | PIND1  | PIND0  |

| DDRD               | DDRD7  | DDRD6  | DDRD5  | DDRD4  | DDRD3  | DDRD2  | DDRD1  | DDRD0  |

| PORTD              | PORTD7 | PORTD6 | PORTD5 | PORTD4 | PORTD3 | PORTD2 | PORTD1 | PORTD0 |

| PORT C             |        |        |        |        |        |        |        |        |

| PINC               | -      | PINC6  | PINC5  | PINC4  | PINC3  | PINC2  | PINC1  | PINC0  |

| DDRC               | -      | DDRC6  | DDRC5  | DDRC4  | DDRC3  | DDRC2  | DDRC1  | DDRC0  |

| PORTC              | -      | PC6    | PC5    | PC4    | PC3    | PC2    | PC1    | PC0    |

| PORT B             |        |        |        |        |        |        |        |        |

| PINB               | PINB7  | PINB6  | PINB5  | PINB4  | PINB3  | PINB2  | PINB1  | PINB0  |

| DDRB               | DDRB7  | DDRB6  | DDRB5  | DDRB4  | DDRB3  | DDRB2  | DDRB1  | DDRB0  |

| PORTB              | PB7    | PB6    | PB5    | PB4    | PB3    | PB2    | PB1    | PB0    |

| Contrôle des Ports |        |        |        |        |        |        |        |        |

| SFIOR              | -      | -      | -      | -      | ACME   | PUD    | PSR2   | PSR10  |

Figure 1.4: Quartz basse fréquence

#### 1.4.1 Paramétrage et usage des *PORTS*

Pour définir le Port en Entrée ou en Sortie on utilise  $DDR_x$  ( $x = B, C, D$ ).

- On peut positionner des résistances de tirage sur les lignes d'un port.

- Ecriture sur le Port : Si le Port est en sortie l'écriture d'un “0” ou d'un “1” positionnera cette valeur sur le  $PORT_x$ . Chaque *port* de 8 bits est limité à un courant total de 200 mA.

- Lecture sur le Port : de la donnée disponible sur le Port est faite dans  $PIN_x$ . A chaque bit du registre  $PIN_x$  est associée une bascule *D* qui permet de stabiliser la lecture en synchronisant sur un front de l'horloge système. Cette stabilisation se fait au détriment d'un délai de lecture qui correspond à une période d'horloge.

### 1.4.2 Résistance de tirage : Pull-up resistor

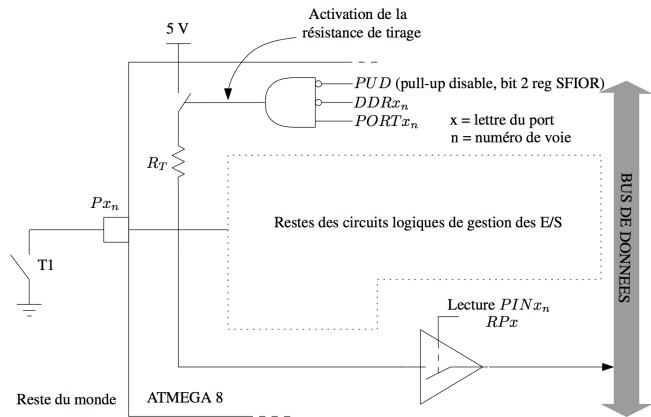

Figure 1.5: Résistances de tirage type "pull-up"

Pour poser des résistances de pull-up il est nécessaire d'avoir les trois conditions suivantes:

- Définir les lignes en entrée ;

- Ecrire un “1” sur ces lignes ;

- PUD mis à zéro dans SFIOR : *SFIOR* & = (1 << *PUD*);

#### Résistances de tirage : le registre *SFIOR*

|       |       |       |   |      |     |      |       |

|-------|-------|-------|---|------|-----|------|-------|

| ADTS2 | ADTS1 | ADTS0 | - | ACME | PUD | PSR2 | PSR10 |

|-------|-------|-------|---|------|-----|------|-------|

*PUD* = “Pull Up Disable”

- 1: Les résistances de tirages sont désactivées, les entrées sont en mode 3-états.

- 0 : Les résistances de tirages sont activées.

### 1.4.3 Registres de manipulation des ports : *DDR<sub>x</sub>*, *PIN<sub>x</sub>* et *PORT<sub>x</sub>*

- *DDR<sub>B</sub>*, *DDR<sub>C</sub>*, *DDR<sub>D</sub>* : Permet de programmer le sens des lignes (1 : sortie, 0 entrée)

- *PORT<sub>B</sub>*, *PORT<sub>C</sub>*, *PORT<sub>D</sub>* : Mémorise l'état des pins, permet l'écriture ou la lecture Ou bien il permet de configurer la résistance de tirage en entrée.

- *PIN<sub>B</sub>*, *PIN<sub>C</sub>*, *PIN<sub>D</sub>* : Permet de lire les valeurs courantes des pattes du port

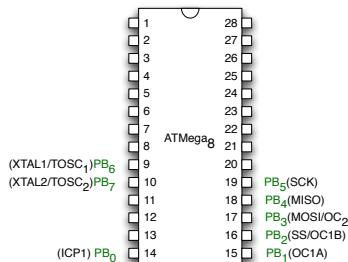

### 1.4.4 Le Port B

- *DDR<sub>B</sub>* : Programme les lignes du port *B*

- $PIN_B$  : Lecture du port  $B$

- $PORT_B$  : Ecriture sur le port  $B$

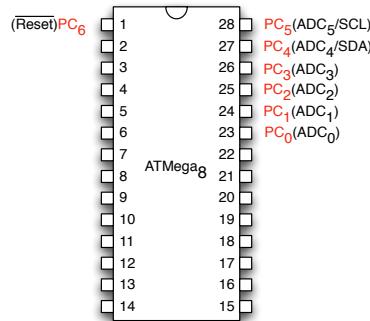

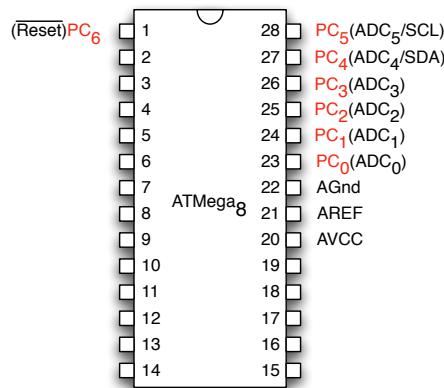

#### 1.4.5 $PORTC$

- $DDR_C$  : Programme les lignes du port  $C$

- $PIN_C$  : Lecture du port  $C$

- $PORT_C$  : Ecriture sur le port  $C$

- $PORTC$  est un port d'entrée-sortie bidirectionnel de 7 bits avec des résistances de pull up.

- Le buffer de sortie du  $PORTC$  a la capacité d'être à la fois source ou drain de courant.

- En entrée les pattes sont tirés à la masse si les résistances de pull-up sont activées.

- Les pins de C sont en 3-états quand un reset survient.

- $PORTC_6 = \overline{RESET}$  si le fusible  $RSTDISBL$  est à 1, alors la ligne est disponible en E/S

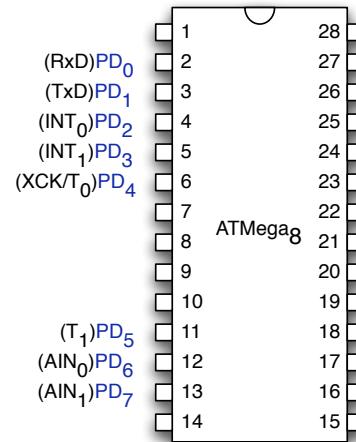

#### 1.4.6 $PORTD$

- $DDRD$  : Programme les lignes du port  $D$

- $PIND$  : Lecture du port  $D$

- $PORTD$  : Ecriture sur le port  $D$

## 1.4.7 Lecture et écriture sur un port

### Ecriture sur un Port

- Pour écrire sur un *port* on déclare une ou plusieurs ligne en sortie par un registre.

Exemple : *DDRD*=0xFF; Tout le *port* est déclaré en sortie

- Ensuite on réalise une écriture sur les lignes déclarées en sortie par le registre *PORTD*

Exemple : *PORTD* = 0b00000011; On active les lignes 0 et 1

Exemple d'écriture d'un Port :

```

int main(void) {

DDRD = 0xFF;      // port D en sortie

PORTD = 0x7A;      //Allume leds 1,3,4,5,6

while(1){          //boucle infinie

PORTD ^= 0x7A; // ^= : ou-exclusif fait clignoter les leds

_delay_ms(20);

}

}

```

## 1.4.8 Lecture d'un Port

- Pour lire sur un *port* on déclare une ou plusieurs ligne en entrée par le registre *DDR<sub>x</sub>*.

Exemple : *DDRD*=0x00; Tout le *port* D est déclaré en entrée

- Ensuite on réalise une lecture sur les lignes déclarées en sortie par le registre *PIN<sub>x</sub>* dans une variable de type entier.

Exemple : *int lu =PIND*; On active les lignes 0 et 1

Exemple d'écriture et d'écriture d'un Port :

```

int main(void) {

DDRC = 0x00; // \pc1 en entrée

DDRD = 0xFF; // port D en sortie

int lu;

while(1){      //boucle infinie

lu = PINC,

PORTD = lu; //PORTD reçoit PORTC

_delay_ms(20);

}

}

```

## 1.4.9 Fonction de manipulation de bits

```

// Mise à un d'un bit sans affecter les autres bits

PORTD = PORTD | (1<<PORTD4);

PORTD |= (1<<4); // mise à un du bit 4

// Mise à un des 4 bits de poids faible sans affecter les autres bits

PORTB = PORTB | 0x0F // ou

PORTB |= 0x0F;

// Mise à zero d'un bit sans affecter les autres bits

PORTB &= ~(1<<PB3); // mise à zero du bit 3

// Mise à zero de 4 bits sans affecter les autres bits

PORTB &= 0x0F; // mise à zero des 4 bits de poids Fort

// Commutation du bit 4 sans affecter les autres bits

PORTD = PORTD^0x10;

PORTD ^= 0x10;

```

# Chapter 2

## Conversion Analogique

### 2.1 Le Comparateur Analogique

#### 2.1.1 Fonctionnement global

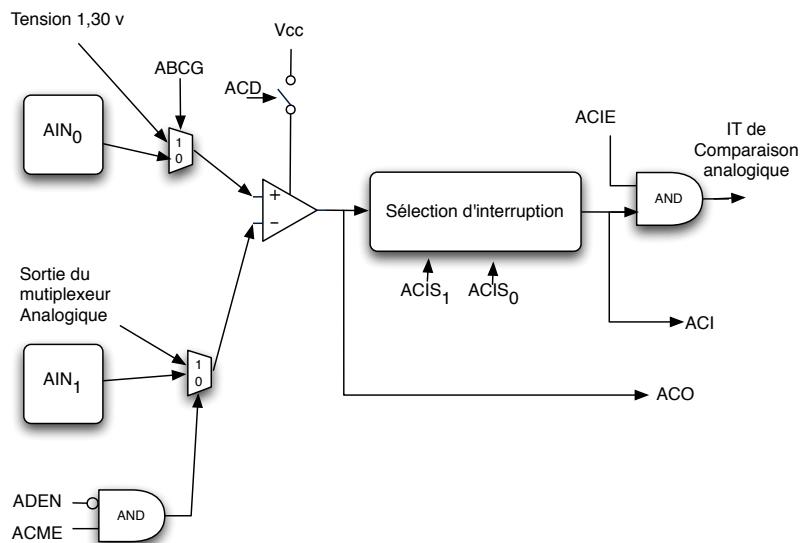

Cet élément offre la possibilité de comparer deux valeurs analogiques sur les pattes  $PD_6$  et  $PD_7$ .  $AIN_0 (PD_6)$  est appelé broche positive et  $AIN_1 (PD_7)$  broche négative. Lorsque  $AIN_0 > AIN_1$  alors  $ACO \leftarrow 1$ , on peut alors déclencher une *interruption* (avec bit  $ACIE = 1$ ) de comparaison.

On a de plus, la possibilité de changer la référence "négative" :  $AIN_1$  par l'une des broches  $ADC_0, ADC_1, \dots, ADC_5$ . De plus, l'utilisateur peut sélectionner comme évènement de déclenchement, un front montant, un front descendant ou une inversion.

En outre, toute entrée  $ADC_5, \dots, ADC_0$  peut jouer le rôle de  $AIN_1$ . Pour réaliser cela il faut positionner à un le bit de multiplexage  $ACME$  du registre  $SFIOR$ , et mettre  $ADEN$  à un du registre  $ADCSRA$  on a alors les  $MUX_{2..0}$  du registre  $ADMUX$ .

Les bits ***MUX*** qui remplacent ***AIN*<sub>1</sub>** selon le tableau suivant :

| <b><i>ACME</i></b> | <b><i>ADEN</i></b> | <b><i>MUX2 : 0</i></b> | <b><i>AIN0</i></b>            |

|--------------------|--------------------|------------------------|-------------------------------|

| 0                  | <i>x</i>           | <i>xxx</i>             | <b><i>AIN1</i></b>            |

| 1                  | 1                  | <i>xxx</i>             | <b><i>AIN1</i></b>            |

| 1                  | 0                  | 000                    | <b><i>ADC</i><sub>0</sub></b> |

| 1                  | 0                  | 001                    | <b><i>ADC</i><sub>1</sub></b> |

| 1                  | 0                  | 010                    | <b><i>ADC</i><sub>2</sub></b> |

| 1                  | 0                  | 011                    | <b><i>ADC</i><sub>3</sub></b> |

| 1                  | 0                  | 100                    | <b><i>ADC</i><sub>4</sub></b> |

| 1                  | 0                  | 101                    | <b><i>ADC</i><sub>5</sub></b> |

| 1                  | 0                  | 110                    | <b><i>ADC</i><sub>6</sub></b> |

| 1                  | 0                  | 111                    | <b><i>ADC</i><sub>7</sub></b> |

## 2.1.2 Les registres

### Registre ACSR: Analog Comparator Status Register ACSR

|                   |   |                   |                   |                    |                    |                     |                     |

|-------------------|---|-------------------|-------------------|--------------------|--------------------|---------------------|---------------------|

| <b><i>ACD</i></b> | - | <b><i>ACO</i></b> | <b><i>ACI</i></b> | <b><i>ACIE</i></b> | <b><i>ACIC</i></b> | <b><i>ACIS1</i></b> | <b><i>ACIS0</i></b> |

|-------------------|---|-------------------|-------------------|--------------------|--------------------|---------------------|---------------------|

- ***ACD*** Analog Comparator Disable : Bit de mise en marche du comparateur analogique,

- 0 : mise en marche,

- 1 : arrêt

- ***ACO*** Analog Comparator Output : Contient le résultat de la comparaison : si  $VAIN_0 > VAIN_1$  alors ***ACO*** = 1.

- ***ACI*** : Analog Comparator Interrupt : Flag Bit de demande d'interruption (bit raz ds le sp d'IT)

- Condition IT : ***ACIS1*** et ***ACI10***). Ce bit est remis à 0 automatiquement après le traitement de l'interruption

- Masque d'IT : ***ACIE***.

- ***ACIE*** Analog Comparator Interrupt enable : Bit de validation de l'interruption *ANA\_COMP*.

- ***ACIC*** : Analog Comparator Input Capture Enable : La mise à 1 de ce bit connecte la sortie du comparateur à l'entrée de capture du Timer1.

- ***ACIS1*** et ***ACI10*** gère le comportement de la sortie ***AC<sub>0</sub>*** :

| Activation de <b><i>AC<sub>0</sub></i></b> | <b><i>ACIS1</i></b> | <b><i>ACIS0</i></b> |

|--------------------------------------------|---------------------|---------------------|

| $1 \rightarrow 0$ ou $0 \rightarrow 1$     | 0                   | 0                   |

| non utilisé                                | 0                   | 1                   |

| <i>front montant</i>                       | 0                   | 0                   |

| <i>front descendant</i>                    | 1                   | 1                   |

### Registre

|                     |                     |                     |   |                    |                   |                    |                     |

|---------------------|---------------------|---------------------|---|--------------------|-------------------|--------------------|---------------------|

| <b><i>ADTS2</i></b> | <b><i>ADTS1</i></b> | <b><i>ADTS0</i></b> | - | <b><i>ACME</i></b> | <b><i>PUD</i></b> | <b><i>PSR2</i></b> | <b><i>PSR10</i></b> |

|---------------------|---------------------|---------------------|---|--------------------|-------------------|--------------------|---------------------|

***ACME*** Analog Comparator Multiplexer Enable

- Quand ***ACME***= 1 et ***ADC*** est éteint (***ADEN*** = 0 et ***ADSC*** = 0) alors le multiplexeur ***ADC*** choisit l'entrée négative du comparateur analogique.

- Quand ***ACME***= 0 alors ***AIN*<sub>1</sub>**est appliqué à l'entrée négative du comparateur analogique.

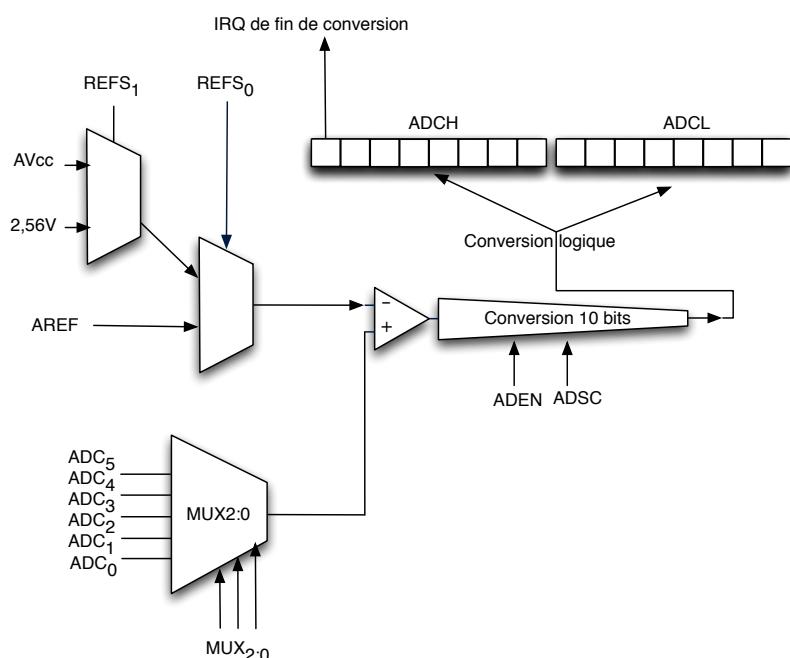

## 2.2 Le Convertisseur Analogique-Numérique : ADC

Le convertisseur (ADC) convertit une tension d'entrée analogique en une valeur à 10 bits digitale par approximations successives. Il possède 6 entrées simultanées avec une non-linéarité inférieure à  $+/- 2 \text{ LSB}$  avec une erreur à 0 V inférieure à 1 LSB. Le résultat de la conversion est positionné dans les registres Analog to Digital Converter High (ADCH) et Analog to Digital Converter Low (ADCL).

Le temps de conversion prend au minimum 13 cycles d'horloge. De plus, le convertisseur a une alimentation découpée du micro :  $AV_{cc}$  tq  $AV_{cc} \in [V_{cc} - 0,3, V_{cc} + 0,3]$  :  $V_{cc}$  est la tension de référence qui peut être externe ou interne :  $AREF$  ou  $AV_{cc}$  ou  $= 2,56 \text{ v.}$

### 2.2.1 Fonctionnement et caractéristiques

On peut le programmer en générant une interruption de fin de conversion. De plus, il est possible de faire fonctionner en limitant le bruit en mode de sommeil. Le résultat de la conversion numérique est donné par la relation :

$$\text{Résultat numérique} = P. \text{ Entière}(\text{Tension d'entrée}/\text{Tension de référence} * 1024)$$

Ou la tension de référence est soit  $AREF$  soit  $AV_{cc}$  soit 2,56v.

ADC\_0= 2.5 V, AREF = 3.3 V

ADCH-ADCL = PE(2.5/3.3 x 1024) = 774

**Réduction des bruits lors de la conversion** Pour réduire au maximum la précision de la conversions on pourra :

- Mettre en sommeil l'unité centrale avant le lancement d'une conversion.

- Découpler soigneusement l'alimentation  $AV_{cc}$  avec des condensateurs.

- Règles élémentaires du routage : connexions courtes, plan de masse, ...

- Effectuer un filtre numérique des résultats (amortissement, moyenne, ...).

La valeur minimale de conversion est  $GND$  tandis que la valeur maximale est soit la tension sur la broche  $AREF$  soit la tension sur la broche  $AV_{cc}$  ou bien une tension interne de 2,56 V (cf bits  $REFS_n$ ).

Chacune des 6 broches d'entrée  $ADC$  peuvent être choisies comme des entrées simples de l' $ADC$ . De plus, l' $ADC$  contient un mécanisme d'échantillonneur-bloqueur qui assure que l'entrée est tenue constante pendant 1,5 cycle d'horloge.

$ADCL$  doit être lu en premier puis  $ADCH$  pour assurer la cohérence des données qui appartiennent à la même conversion. Une fois  $ADCL$  lu, l'accès aux registres de commandes est bloqué afin d'empêcher une nouvelle conversion tant que  $ADCH$  n'est pas lu. Quand  $ADCH$  est lu, l' $ADC$  est à nouveau opérationnel. L' $ADC$  a sa propre interruption qui peut être déclenchée quand une conversion est achevée. La lecture de l' $ADCL$  et d' $ADCH$  interdit l'accès aux registres de commande de l' $ADC$ , mais si une *interruption* de fin conversion se produit alors que la lecture précédente n'a pas été encore faite le résultat sera perdu. Il faut donc faire attention à lire rapidement un résultat de conversion.

## Programmation

L'ensemble des registres à programmer l' $ADC$  est  $ADMUX$ ,  $ADCSRA$ ,  $ADCH$ ,  $ADCL$ , étudions  $ADEN$   $ADSC$   $ADATE$   $ADID$  ( $ADCSRA$ ) :

|        |        |        |        |        |         |         |         |

|--------|--------|--------|--------|--------|---------|---------|---------|

| $ADEN$ | $ADSC$ | $ADFR$ | $ADIF$ | $ADIE$ | $ADPS2$ | $ADPS1$ | $ADPS0$ |

|--------|--------|--------|--------|--------|---------|---------|---------|

- L' $ADC$  est activé avec le bit  $ADEN$ .

- La référence de tension et le choix du canal d'entrée n'entrera pas en vigueur quand  $ADEN$  est mis à 1, il faut d'abord désactiver  $ADEN$ .

- $ADC$  produit un résultat sur 10 bits qui est présenté dans les registres  $ADCH$  et  $ADCL$ .

- Par défaut, le résultat est présenté ajusté à droite, mais peut facultativement être présenté ajusté à gauche en mettant le bit  $ADLAR$  à un dans  $ADMUX$ . Pour un résultat sur 8 bits et un ajustement à gauche, la lecture du registre  $ADCH$  est suffisante.

## Lancement d'une conversion

**Début d'une conversion** Une conversion simple est lancée par  $ADSC \leftarrow 1$  ( $ADSC \in ADCSRA$ ).

Si l'on change le canal tandis qu'une conversion est en cours, l' $ADC$  finira la conversion actuelle avant l'exécution du changement de canal.

**Fin de conversion** Dès lors, qu'une conversion est en cours,  $ADSC$  reste à un tant que la conversion se réalise et il redescend à 0 quand la conversion est achevée. Quand une conversion est finie, le résultat est écrit dans les registres de données  $ADCH$  et  $ADCL$  et  $ADIF$  est mis à 1. Le programme peut alors lancer  $ADSC$  de nouveau et une nouvelle conversion sera amorcée sur le premier front montant de l'horloge.

**Durée d'une conversion** Une conversion simple commence par  $ADSC \leftarrow 1 \in ADCSRA$  puis en attendant le front montant suivant du cycle d'horloge  $ADC$ . Une conversion normale prend 13 cycles d'horloge.

La première conversion après l'allumage de l' $ADC$  :  $ADEN$  mis alors à 1 dans  $ADCSRA$ .

## 2.2.2 Les différentes méthodes de programmation d'une conversion

### Conversion échantillonnée

Pour ce mode on va utiliser un **timer** qui va définir une période d'échantillonnage. On va associer à une *interruption* de débordement de ce **timer** dans laquelle on va déclencher la conversion analogique-numérique. Un exemple de codage est donnée dans la section suivante (cf section ??).

### Free Running mode : Mode de fonctionnement libre

Dans ce mode, l'**ADC** échantillonne en permanence, sans aucune action du programmeur autre que le lancement initial, et met à jour les registres de données (**ADCH** et **ADCL**). Ce mode est positionné par la valeur 1 dans **ADFR** ∈ **ADCSRA**. La première conversion doit être lancée par **ADSC** ∈ **ADCSRA**. Dans ce mode l'**ADC** effectue des conversions sans se préoccuper du flag d'*interruption* **ADIF**. Un exemple de codage est donnée dans la section suivante (cf section 2.2.3).

### Conversion avec attente active

Pour ce mode on va définir une fonction ducture qui retournera un entier image de la conversion. L'attente active est du au fait que, après avoir lancée la conversion par **ADSC**. Un exemple de codage est donnée dans la section suivante (cf section ??).

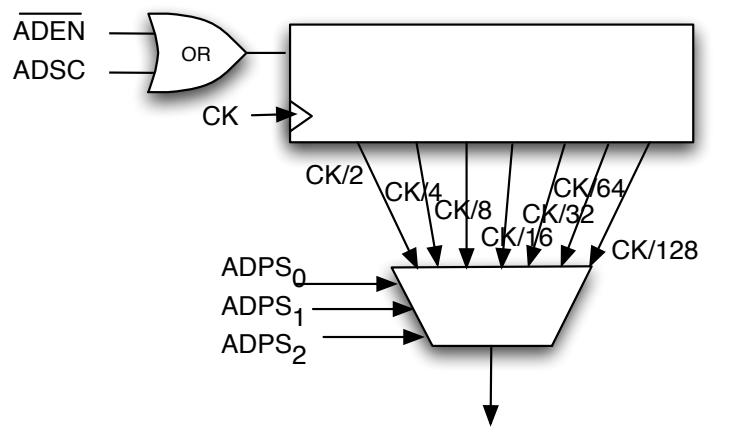

**Aspects numériques** Par défaut, la fréquence d'horloge d'entrée est entre 50  $kHz$  et 200  $kHz$  pour obtenir la résolution maximale. Si une résolution plus basse que 10 bits est nécessaire, la fréquence d'horloge d'entrée de l'**ADC** peut alors être plus haute que 200  $kHz$ .

**Temps de conversion** Le temps de conversion qui est égal à 13 fois l'horloge système, peut, de plus, être multiplié, par un facteur de pré-division (cf bits **ADPS<sub>2-0</sub>**). Le module **ADC** contient un pré-diviseur qui produit une fréquence d'horloge acceptable pour l'**ADC** à partir de celle du **Control Process Unit (CPU)**. La Mise en marche pré-diviseur se fait par **ADPS** ∈ **ADCSRA** et le pré-diviseur commence à compter dès que l'**ADC** est allumé en mettant le bit **ADEN** à 1 dans **ADCSRA**.

## 2.2.3 Les Registres de l'**ADC** : **ADMUX**, **ADCSRA**, **ADCH**, **ADCL**

- **ADMUX**

|                         |                         |              |   |                        |                        |                        |                        |

|-------------------------|-------------------------|--------------|---|------------------------|------------------------|------------------------|------------------------|

| <b>REFS<sub>1</sub></b> | <b>REFS<sub>0</sub></b> | <b>ADLAR</b> | - | <b>MUX<sub>3</sub></b> | <b>MUX<sub>2</sub></b> | <b>MUX<sub>1</sub></b> | <b>MUX<sub>0</sub></b> |

|-------------------------|-------------------------|--------------|---|------------------------|------------------------|------------------------|------------------------|

- $REFS_1, REFS_0$

| $REFS_1$ | $REFS_0$ | Tension de Référence                     |

|----------|----------|------------------------------------------|

| 0        | 0        | AREF                                     |

| 0        | 1        | $AV_{cc}$ avec capacité externe sur AREF |

| 1        | 0        | non utilisé                              |

| 1        | 1        | 2,56 v                                   |

- $ADLAR$  : ADC Left Adjust Result Ajustement à gauche à 1 ou à droite à 0 du résultat dans le registre  $ADCL$  et  $ADCH$ .

- $MUX_{3,2,1,0}$  : Choix du canal ADC .

- $ADCSRA$

|        |        |        |        |        |          |          |          |

|--------|--------|--------|--------|--------|----------|----------|----------|

| $ADEN$ | $ADSC$ | $ADFR$ | $ADIF$ | $ADIE$ | $ADPS_2$ | $ADPS_1$ | $ADPS_0$ |

|--------|--------|--------|--------|--------|----------|----------|----------|

- $ADEN$  : (AD ENable) Mise en marche du convertisseur avec la mise à 1 du bit, l'arrêt avec la mise à 0, la conversion en cours sera terminée.

- $ADSC$  : (AD Start Conversion) Lancement de la conversion de la voie sélectionnée (retourne à 0 en fin de conversion). En mode simple conversion, il faut remettre à 1 à chaque nouvelle conversion. En mode libre, la première conversion dure 25 cycles puis les suivantes 15, il n'est pas nécessaire de remettre le bit à 1 à chaque conversion.

- $ADFR$  : (Analog Digital Free Running Mode) La mise à 1 de ce bit permet de mettre en le convertisseur en mode conversion libre : mode de fonctionnement où les conversions ont lieu en permanence sans avoir besoin d'être relancées.

- $ADIF$  : (AD Interrupt Flag) Passe à 1 une fois la conversion terminée et déclenche l'interruption si  $ADIE = 1$ . Ce bit repasse automatiquement à 0 lors du traitement de la routine d'interruption.

- $ADIE$  : “AD Interrupt Enable” : Validation de l'interruption du convertisseur.

- $ADPS_2, \dots, ADPS_0$  : Bits de Sélection du "Prescaler": facteur de pré-division de l'horloge interne du convertisseur en fonction du quartz : rien,2,4,8,16,32,64,128.

- $ADCH - ADCL$ :

- Avec  $ADLAR = 0$  : On cherche un résultat sur 10 bits

|         |         |         |         |         |         |         |         |

|---------|---------|---------|---------|---------|---------|---------|---------|

| -       | -       | -       | -       | -       | -       | $ADC_9$ | $ADC_8$ |

| $ADC_7$ | $ADC_6$ | $ADC_5$ | $ADC_4$ | $ADC_3$ | $ADC_2$ | $ADC_1$ | $ADC_0$ |

```

int L    = ADCL;

int H    = ADCH;

int res = (H<<8)+L;

```

- Avec  $ADLAR = 1$  : On cherche un résultat sur 8 bits en laissant tomber  $ADCL$

|         |         |         |         |         |         |         |         |

|---------|---------|---------|---------|---------|---------|---------|---------|

| $ADC_9$ | $ADC_8$ | $ADC_7$ | $ADC_6$ | $ADC_5$ | $ADC_4$ | $ADC_3$ | $ADC_2$ |

| $ADC_1$ | $ADC_0$ | -       | -       | -       | -       | -       | -       |

```

int res = ADCH;

```

## Programmes relatifs à l'ADC

- 1- Mode scrutatif : attente active. La led qui doit clignoter sur  $PB_0$ .

```

volatile int lu; // variable globale

void lecture_analogique_scrutative(){

char L;

ADCSRA |= (1<<ADSC);

while (ADCSRA & (1<<ADSC)) {};

lu=ADCH; // lecture sur 8 bits

}

int main(void){

DDRB=0x1F; DDRC=0x00; // C : entree, B : Sortie

ADMUX=(1<<ADLAR); // ajust Gauch, PC0 entree analog.

ADCSRA= (1<<ADEN); // Mise On ADC

do {

_delay_ms(200);

lecture_analogique_scrutative();

} while(1);

return(0);

}

```

-2- Mode échantillonné : On réalise ici, un déclenchement échantillonée par le **timer** 1, de la conversion analogique

```

volatile int F;

ISR(ADC_vect){char L=ADCL;F=ADCH; }

ISR(TIMER1_OVF_vect) {ADCSRA |= (1<<ADSC);PORTB^=1;}

int main(void){

DDRB=0x1F;DDRC=0x00;

ADMUX=(1<<ADLAR); // ajust Gauche, Lecture sur PC0

ADCSRA= (1<<ADEN)+(1<<ADIE); // mise ON du can, IT CAN

TCCR1A=0;TCCR1B = (1 << CS11); // prediv du \timer\ Fcpu/8

TIMSK = (1<<TOIE1); // Validation It de debordement */

sei(); // toute les its autorisees

do {

PORTB^=1;_delay_ms(50);

}while(1);

return(0);

}

```

-3- Free Running : On lance l'**ADC** une fois ouis on lit à la volée **ADCH** et **ADCL**.

```

int main(void){

int H,L;

DDRB=0x1F; DDRC=0x00;

ADMUX=(1<<ADLAR);

ADCSRA= (1<<ADEN) + (1<<ADSC)+(1<<ADFR);

do {

PORTB^=1;

delai(50);

L=ADCL; H = ADCH;

Res = (H<<8)+L;

} while(1);

return(0);

}

```

-4- Mode bogué : Sans **timer** relance de l'**ADC** dans l'*interruption* de conversion.

```

volatile int F;

ISR(ADC_vect){F=ADCH; ADCSRA |= (1<<ADSC) // Aie !!!

int main(void){

DDRB=0x1F;DDRC=0x00;

ADMUX=(1<<ADLAR); // ajust Gauche, Lecture sur PC0

ADCSRA= (1<<ADEN)+(1<<ADIE); // mise ON du can, IT CAN

sei(); // toute les its autorisees

do {

PORTB^=1; _delay_ms(50);

}while(1);

return(0);

}

```

# Chapter 3

## Les Timers

Les fonctions d'un **timer** concernant d'abord les fonctions de temporisation avec la définition de base de temps, la génération de formes (signaux carrés, *MLI* ) ainsi que le comptage d'événements. Un **timer** permet aussi de mesurer un temps entre deux événements.

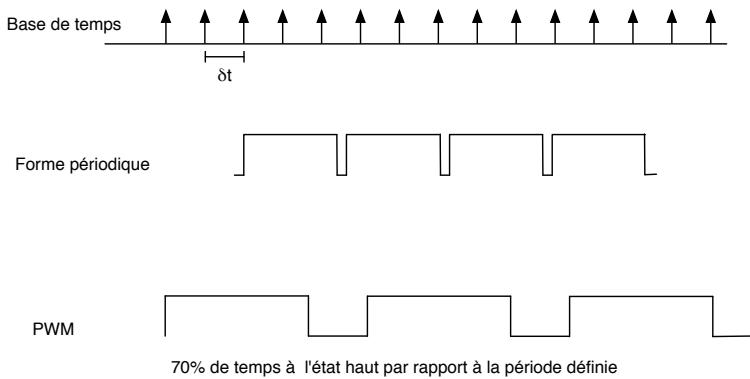

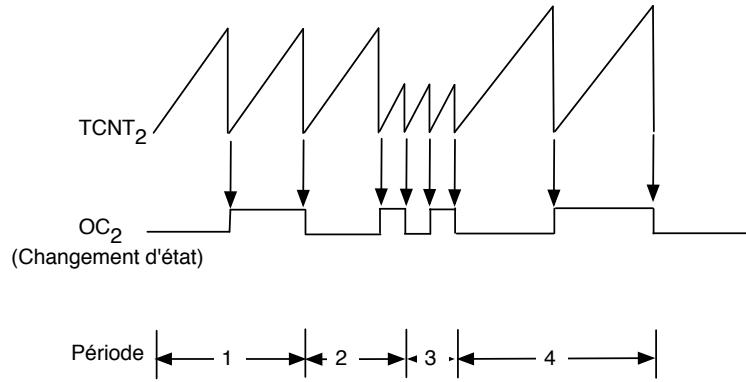

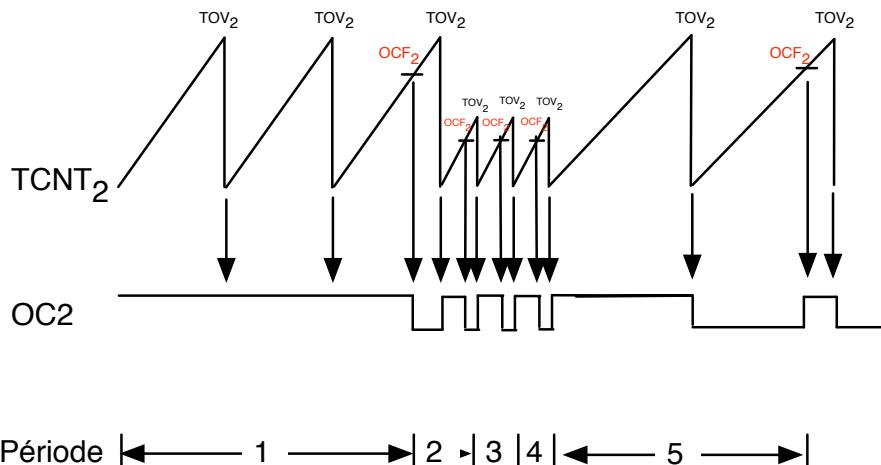

Dans la figure suivante nous illustrons une base de temps et la génération de formes :

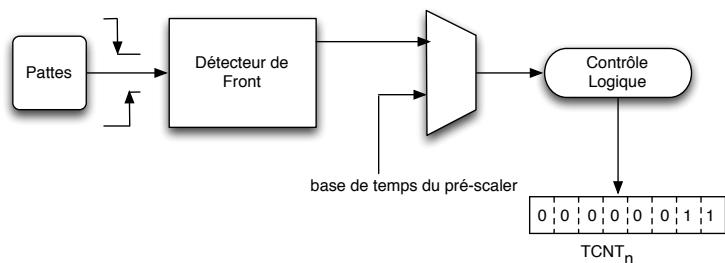

Dans cette figure on décrit le comptage ou la capture d'événements :

L'*ATMEGA8* possède 3 **timers** : **timer 0**, **timer 1** et **timer 2**. Les **timers 0** et **2** sont des **timers** 8 bits tandis que les timers **1** est un **timer** 16 bits. Le **timer 2** est plus élaboré que le **timer 0**, il permet en plus de faire de la *MLI* et de produire une *interruption* de comparaison.

### 3.1 Le **timer 0**

#### 3.1.1 Caractéristiques

Ses fonctions de base

- **timer** à sortie unique

- Générateur de fréquences

- Comptage d'événements externes

- Pré-diviseur d'horloge 10 bits

- Le **timer** 0 se manipule à l'aide de seulement 3 registres :

- $TCNT_0$

- $TCCR_0$

- $TIMSK$

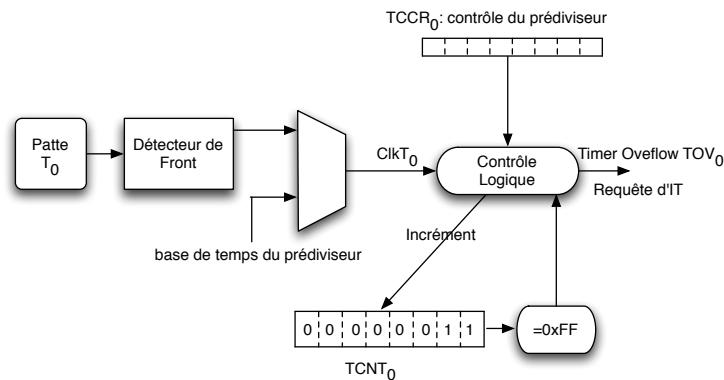

**Aperçu global du timer 0** Le **timer** 0 est un **timer** 8 bits. Un débordement provoque l'événement  $TIMER0\_OVF\_vect$  et la mise à un du drapeau  $TOV_0$  (dans le registre  $TIFR$ ) et possiblement une *interruption* se produit. Le masquage ou l'autorisation de cette *interruption* est réalisé par le bit  $TOIE_0$  du registre  $TIMSK$ . Comme le montre le schéma précédent  $TCNT_0$  s'incrémentera suivant :

- La patte externe **timer** 0

- Ou le pré-diviseur d'horloge. Ce choix étant fait par les bits  $CS0_{2:0} \in TCCR_0$

Figure 3.1: Aperçu de **timer** 0

- Le bloc logique ordonne alors l'incrément du registre  $TCNT_0$ .

- Lorsque  $TCNT_0$  atteint la valeur  $0xFF$  il repasse à la valeur 0 et dans le même temps le bit  $TOV_0$  passe à un.

- $TOV_0$  agit comme un 9<sup>ème</sup> bit.

- Si une *interruption* a été mise en place alors ce bit est **raz** lors de l'exécution du sous-programme d'interruption associé.

### 3.1.2 Les registres associés au **timer** 0 : $TCCR_0$ , $TCNT_0$

- $TCCR_0$

| $CS02$ | $CS01$ | $CS00$ | Description                                         |

|--------|--------|--------|-----------------------------------------------------|

| 0      | 0      | 0      | $T_0$ en pause                                      |

| 0      | 0      | 1      | $clk_{I/O}$ : Horloge Système                       |

| 0      | 1      | 0      | $clk_{I/O}/8$                                       |

| 0      | 1      | 1      | $clk_{I/O}/64$                                      |

| 1      | 0      | 0      | $clk_{I/O}/256$                                     |

| 1      | 0      | 1      | $clk_{I/O}/1024$                                    |

| 1      | 1      | 0      | source externe : front descendant sur la patte $T0$ |

| 1      | 1      | 1      | source externe : front montant sur la patte $T0$    |

**Remarque 3.1.1** Si par ailleurs, la patte est utilisée en entrée Alors un front sur cette patte affectera quand même **timer 0** si les modes 6 ou 7 ont été choisis.

- $TCNT_0$  : Accessible en lecture ou écriture : Registre de comptage courant.

- $TIMSK$

|          |          |           |             |             |          |   |          |

|----------|----------|-----------|-------------|-------------|----------|---|----------|

| $OCIE_2$ | $OCIE_2$ | $TICIE_1$ | $OCIE_{1A}$ | $OCIE_{1B}$ | $TOIE_1$ | - | $TOIE_0$ |

|----------|----------|-----------|-------------|-------------|----------|---|----------|

La condition d'autorisation de l'*interruption* de débordement de **timer 0** est  $TOIE_0 = 1$  ET  $I = 1 \in SR$ ). Sur un débordement de  $TCNT_0$ , on a :

- $TOV_0 \in TIFR$  qui passe à un, et le programme associé à l'*interruption* est alors exécuté.

- $TOV_0$  est alors automatiquement raz dès le début du sous-programme d'IT.

Sinon en mode non interruptif, c.a.d. en mode scrutatif il faut remettre à zéro ce bit **EN Y ECRIVANT UN "1"**.

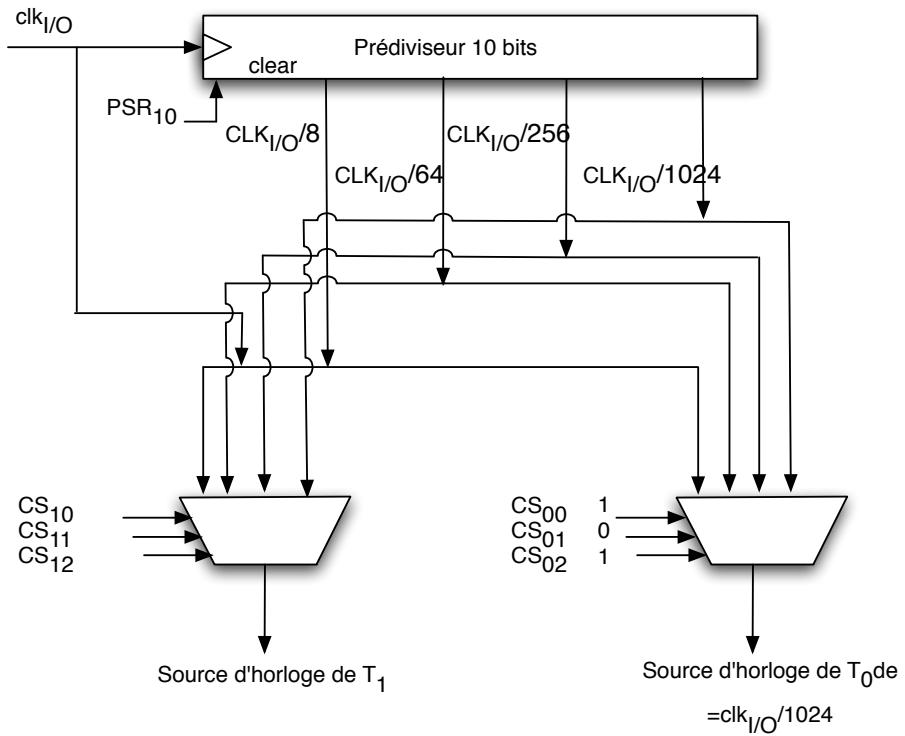

### 3.1.3 Le prédiviseur

Les timers **timer 0** et **timer 1** partagent le même module de pré-division, mais ceux-ci peuvent avoir des fréquences différentes de pré-divisions par rapport à la source d'Horloge Interne. Le Timer/Compteur peut être cadencé directement par l'horloge de système (avec  $CS0_{2:0} \in TCCR_0$  (**timer 0**) ou  $CS1_{2:0} \in TCCR_1$  à 1) permettant une fréquence d'horloge maximale :  $clk_{I/O}$ . Autrement, on pourra choisir un facteur de pré-division suivant :  $clk_{I/O}/8, clk_{I/O}/64, clk_{I/O}/256, clk_{I/O}/1024$ .

Il y a la possibilité d'échantillonner la source externe à travers un détecteur de front qui induira alors un retard de 2.5 à 3.5 cycles d'horloge.

### SFIOR

|                         |                         |                         |   |             |            |                        |                         |

|-------------------------|-------------------------|-------------------------|---|-------------|------------|------------------------|-------------------------|

| <i>ADTS<sub>2</sub></i> | <i>ADTS<sub>1</sub></i> | <i>ADTS<sub>0</sub></i> | - | <i>ACME</i> | <i>PUD</i> | <i>PSR<sub>2</sub></i> | <i>PSR<sub>10</sub></i> |

|-------------------------|-------------------------|-------------------------|---|-------------|------------|------------------------|-------------------------|

- Quand  $PSR_{10} \leftarrow 1$  le prédiviseur de **timer 0** et **timer 1** est **raz**.

- Attention ce prédiviseur est partagé par **timer 0** et **timer 1**, et un **reset** du prédiviseur les affectent tous les 2.

Exemple d'utilisation du **timer** zéro avec la mise en place d'une interruption de débordement :

```

ISR (TIMERO_OVF_vect) {

static int Compteur;

if (Compteur++ == 50) {

Compteur=0;

PortB^=1 // permet de mesurer la periode

}

}

void configTimer0(){

TCCR0 = (1<<CS02) + (1<<CS00) ; // clkio/1024

TIMSK = 1<<TOIE0; // Autorisation IT de debordement

}

int main() {

DDRB=0xFF;

configTimer0();

sei(); // autorise ttes les interruptions

while(1);

}

```

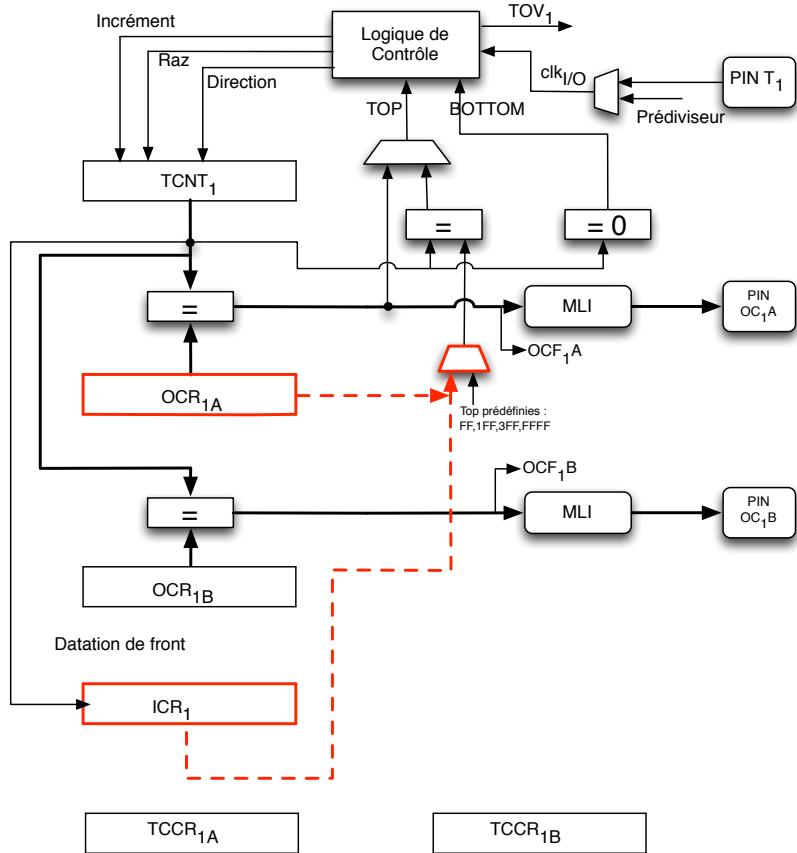

## 3.2 Le **timer** 1

### 3.2.1 Caractéristiques générales

Ses fonctions de base

- **timer** 16 bits ;

- 2 sorties indépendantes de comparaison ;

- Une entrée de capture avec réduction de bruit ;

- 16 modes de *PWM*

- Générateur de fréquence

- Compteur externe d'événements

- 4 sources d'IT : *TOV<sub>1</sub>*, *OCF<sub>1A</sub>*, *OCF<sub>1B</sub>*, *ICF<sub>1</sub>*.

### Les registres 16 bits

- le registre de comptage  $TCNT_1$

- les registre de sortie de comparaison :  $OCR_{1A}$  -  $OCR_{1B}$

- le registre de capture d'entrée  $ICR_1$

### les registres 8 bits

- Les registres de contrôle du timer  $TCCR_{1A}$  -  $TCCR_{1B}$

- le registre de sortie de comparaison :  $OCR_{1A}$  -  $OCR_{1B}$

- le registre de capture d'entrée  $ICR_1$

**Les interruptions du timer 1 :** Tous les signaux d'IT sont visibles depuis  $TIFR$ . Toutes les *interruptions* sont masquables individuellement dans  $TIMSK$

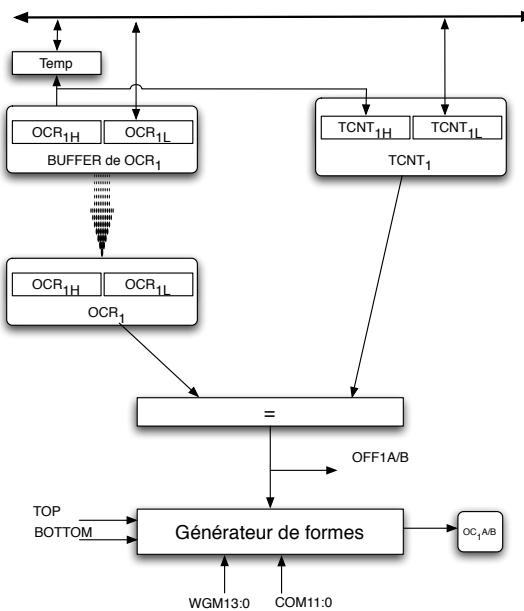

**Contrôle de  $TCNT_1$ :** Le timer 1 peut être fréquencé de façon interne par le prédiviseur ou par une source externe patte **timer 1**. Le bloc logique détermine comment la source est utilisée pour incrémenter ou décrémenter  $TCNT_1$ . Le timer 1 est inactif quand il n'y a aucune source. La source  $clk_{T_1}$  de la figure (en haut à droite de la figure 3.2.1) est sélectionnée par  $CS_{1_{2:0}} \in TCCR_{1B}$ .

**Comparaison de seuil :** Les deux registres de comparaison  $OCR_{1A}$  -  $OCR_{1B}$  sont utilisés comme des seuils qui sont comparés avec  $TCNT_1$ . Le résultat de ces comparaisons peut être utilisé pour générer une forme de type PWM ou bien une fréquence variable sur les pattes  $OC1_A$ ,  $OC1_B$ . Ces comparaisons d'égalité vont positionner les flags  $OCF_{1A}$  ou  $OCF_{1B}$  qui peuvent alors être utilisés pour générer l'*interrupt* correspondante.

**La capture :** Le registre de capture d'entrée  $ICR_1$  peut capturer un événement (front) sur la patte  $ICP_1$ . Cette partie inclut un filtre réducteur de bruit évitant la capture de fronts parasites.

**Le choix de la valeur maximum :** La valeur  $TOP$  est soit le maximum du **timer** (0xFFFF) ou bien une valeur définie dans  $ICR_1$  ou  $OCR_{1A}$ . L'utilisation de  $OCR_{1A}$  pour définir la valeur  $TOP$ , bloque la génération de PWM pour la sortie  $OC1A$ . Lorsque l'on utilise  $ICR_1$  pour définir la valeur  $TOP$  les deux sorties PWM sont alors disponibles ( $OCR_{1A}$  et  $OCR_{1B}$ ), par contre l'entrée de capture n'est plus disponible.

|          |                                                                                                                   |

|----------|-------------------------------------------------------------------------------------------------------------------|

| $BOTTOM$ | $BOTTOM = 0x0000$                                                                                                 |

| $MAX$    | $MAX = 0xFFFF$                                                                                                    |

| $TOP$    | $TCNT_1$ atteind $TOP$<br>c.a.d quand il atteint soit :<br>– 0xFF, 0x1FF, 0x3FF<br>– $OCR_{1A}$ , ou bien $ICR_1$ |

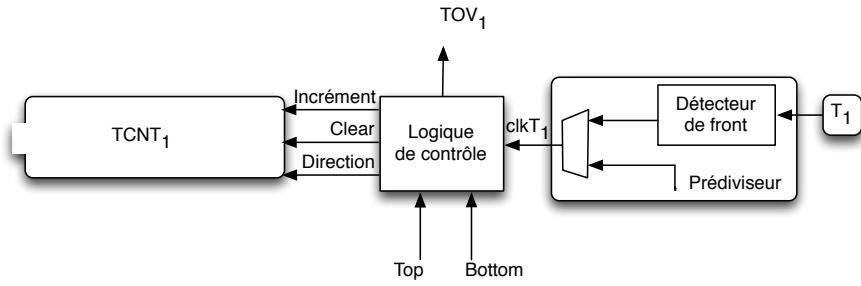

### Fonctionnement de l'Unité de Comptage

Le registre  $TCNT_1$  est piloté par le bloc logique via les signaux *clear*, *increment* ou *decrement* et par la source  $clkT_1$ .  $clkT_1$  peut être généré par une source externe ou interne selon les bits  $CS12:0$ . Quand  $CS12:0 = 0$ , le **timer** 1 est arrêté, la valeur de  $TCNT_1$  étant toujours accessible par le **CPU**. Une écriture par le **CPU** sur  $TCNT_1$  a la priorité sur toute autre opération.

La séquence de comptage peut alors déterminer une forme d'onde (waveform) sur la patte  $OC1A$  selon les bits  $WGM13:0$  des registres  $TCCR_{1A}$  et  $TCCR_{1B}$ . Les formes d'onde dépendent en fait des modes de comptage (cf section 3.2.3) sur  $TCNT_1$ . Le bit de débordement  $TOV_1$  dépend aussi du mode choisi sur  $WGM13:0$ .

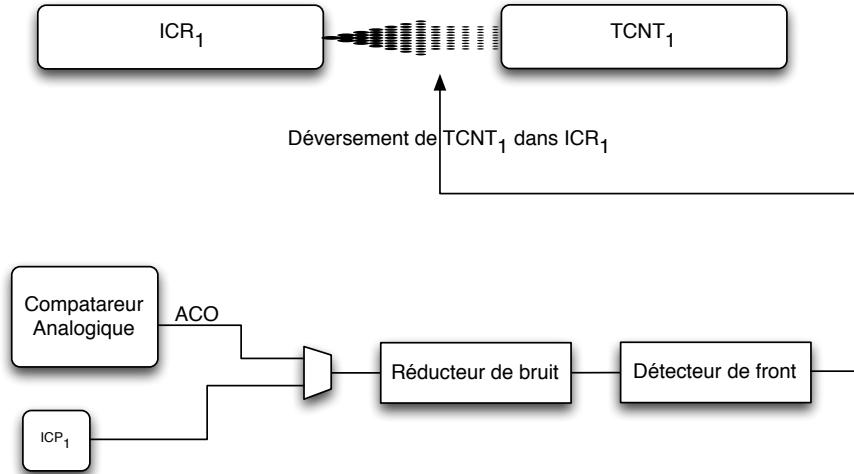

### Unité de capture

L'unité de capture peut capturer des événements externes en leur attachant une étiquette temporelle<sup>1</sup> attachée à cette occurrence. Le signal externe indiquant l'occurrence d'un ou de plusieurs événements est disponible sur la patte  $ICP_1$  ou par le comparateur analogique. Les étiquettes temporelles peuvent être utilisées pour calculer une fréquence, un rapport cyclique ou d'autres. Ces étiquettes temporelles sont parfois utilisées pour créer un "log" d'événements.

**Aperçu de l'Unité de Capture** Quand un événement (front) se produit (cf figure 3.2.1) sur  $ICP_1$ , ou sur  $ACO$ , ce signal passe par le réducteur de bruit et le détecteur de front. Si il passe cet étage, il déclenche l'écriture de  $TCNT_1$  dans  $ICR_1$ .  $TCNT_1$  constitue alors ce que l'on appelle une étiquette temporelle. Dans le même temps le drapeau  $ICF_1$  passe à un.

<sup>1</sup>qui est la valeur courante de  $TCNT_1$

Figure 3.2: Unité de capture

En mode interruptif, Si  $TICIE_1$  passe à un, une *interruption* de capture est déclenchée.  $ICF_1$  est automatiquement remis à zéro dans le sous-programme d'IT.

**Remarque 3.2.1**  $ICR_1$  ne peut être mis à jour que lorsque l'on utilise le mode qui utilise  $ICR_1$  fixant la valeur  $TOP$ . Dans ce cas, les bits  $WGM1_{3:0}$  doivent être positionnés avant que  $ICR_1$  soit initialisé avec la valeur  $TOP$ . On écrira dans  $ICR_1$  d'abord l'octet de poids faible puis le poids Fort.

**La source de capture :** La patte de capture est  $ICP1$ . Cette source peut aussi être connectée au comparateur analogique. Le comparateur est sélectionné avec le bit  $ACIC$  du registre  $ACS$ .

**Remarque 3.2.2** Attention, changer la source peut provoquer une capture, le flag  $ICF$  doit donc être **raz** après ce changement.

Les pattes  $ICP_1$  et la patte de sortie  $ACO$  sont échantillonnées avec les mêmes techniques déjà évoquées : Le détecteur de front est identique. Quand le réducteur de bruit est activé, de la logique est rajoutée avant le détecteur de front ce qui ralentit le signal de 4 cycles d'horloge. Une entrée de capture peut être déclenchée par programme en contrôlant le  $PORTC$  contenant la patte  $ICP1$ .

**Réducteur de bruit** C'est en fait un filtre numérique qui délivre la sortie **ssi** les 4 signaux échantillonnés consécutifs sont égaux. Le réducteur est activé par le bite  $ICNC_1$  du registre  $TCCR_{1B}$ .

**Capture des événements** Tout événement capturé écrase le précédent même si il n'a pas été traité par le **CPU**. Aussi, dans un sous-programme d'*interruption* il faudra lire  $ICR_1$  au plus tôt. On prendra garde à ne pas changer la valeur  $TOP$  lors de l'utilisation de capture. Lors de la mesure d'un signal de type *PWM*, la détection est changée après chaque capture et cela doit donc être fait aussitôt que  $ICR_1$  a été lu.

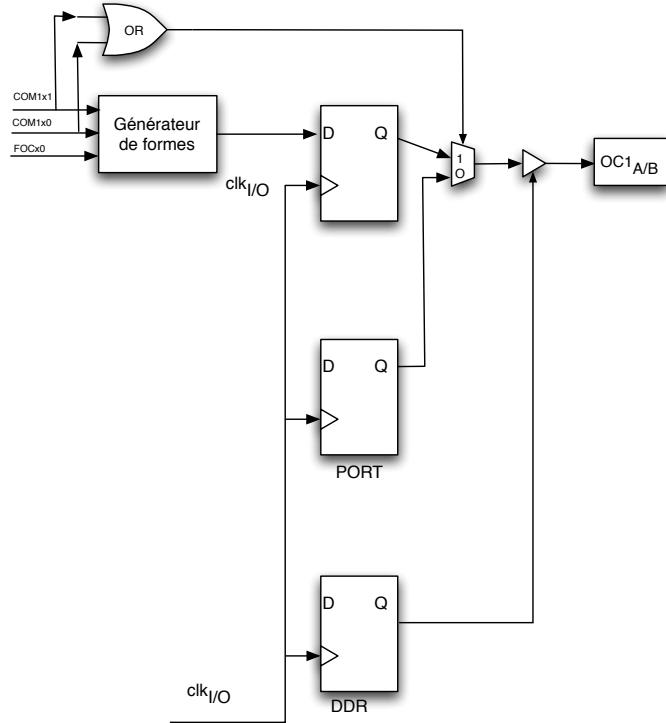

### Unité de Comparaison de sorties

Les sorties  $OC1A/B$  sont contrôlées par les bits  $COM1x1 : 0$ . Un de ces bits à un provoque la sortie du générateur de forme.

Figure 3.3: Contrôle de la sortie du comparateur

La forme produite sur les pattes *OC1A* ou *OC1B* dépend des bits *WGM1<sub>3:0</sub>* et des modes de comparaison défini par *COM1x1 : 0*, ainsi que des valeurs pour *TOP* et *BOTTOM*. Il faut noter que cette figure montre que les pattes *OC1A* ou *OC1B* doivent avoir été déclarées en sortie à l'aide du registre *DDR*.

### 3.2.2 Les 16 modes du timer 1

Le Comparateur permet de définir la valeur *TOP* de *TCNT<sub>1</sub>*. Le comparateur peut fonctionner suivant différents modes.

Figure 3.4: Unité de comparaison

## Initialisation des registres et pattes de sorties

***TCNT<sub>1</sub>*** : L'écriture dans ***TCNT<sub>1</sub>*** quel que soit le mode va bloquer les comparaisons pour un cycle d'horloge. Il y a des risques à changer ***TCNT<sub>1</sub>*** en utilisant le comparateur : Si la valeur écrite dans ***TCNT<sub>1</sub>*** est égale à ***OCR<sub>1A</sub>*** ou ***OCR<sub>1B</sub>*** alors le résultat de la comparaison sera perdu. Il ne faut pas écrire dans ***TCNT<sub>1</sub>*** une valeur égale à ***TOP*** en mode PWM à valeur variable. La comparaison avec ***TOP*** échouera alors et continuera jusqu'à 0xFFFF. Même effet si l'on écrit dans ***TCNT<sub>1</sub>*** une valeur égale à ***BOTTOM*** en décomptant.

Concernant les pattes OC1A et OC1B, il faut faire attention à positionner OC1A et OC1B, en sortie (***PB<sub>6</sub>***, ***PB<sub>7</sub>***) avant de produire une MLI par l'écriture de ***DDR<sub>B</sub>***.

Le générateur de formes est défini par les bits ***COM1x1 : 0*** qui permettent de définir 16 modes regroupés 5 catégories :

- Normal

- *CTC*

- *PWM* rapide

- Phase correcte *PWM*

- Phase et fréquence correcte *PWM*

modes normal, *CTC*, fast *PWM* , ... En mode *PWM* ***COM1x1 : 0*** définissent si la *PWM* est inversée ou non. Les modes sont complètement définis avec : ***WGM1<sub>3:0</sub>*** et ***COM1x1 : 0***.

### 3.2.3 Les Modes du générateur de formes

Les 16 différents modes sont déterminés par les bits : ***WGM1<sub>3:0</sub>***

#### a) Le mode Normal : ***WGM1<sub>3:0</sub>***=0

La sortie ***OC<sub>1A</sub>*** commute à chaque fois que ***TCNT<sub>1</sub>*** atteint la valeur ***TOP*** (si ***COM1A<sub>1:0</sub>***= 1)

- Dans ce mode la fréquence max est :

$$f_{OC1A} = \frac{f_{clk_{I/O}}}{2}$$

- Sinon la fréquence est définie par :

$$f_{OC1A} = \frac{f_{clk_{I/O}}}{2.N.(1 + OCR1_A)}$$

*N* représente le facteur de prédivision (1,8,64,256,1024)

**Attention** à ne pas changer la valeur ***TOP*** avec une valeur inférieure à la valeur courante du comparateur ***OCR<sub>1A</sub>***.

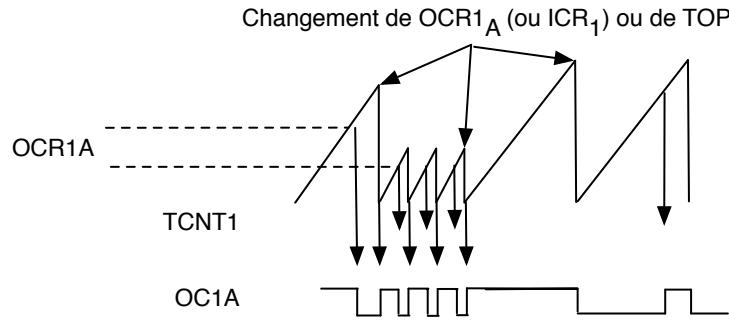

#### c) Le mode *PWM* rapide ***WGM1<sub>3:0</sub>***=5,6,7,14 ou 15

Cette *PWM* permet de générer de plus hautes fréquences. Elle est dite à simple pente et on peut ici avoir 2 commutations de la sortie sur la même pente. Ici, ***TCNT<sub>1</sub>*** compte de ***BOTTOM*** à ***TOP*** et fait alors une comparaison avec un seuil (***OCR<sub>1A</sub>***), pendant la montée puis revient à ***BOTTOM***.

#### Sortie

- En mode non inversé, la sortie est **raz** sur égalité avec ***OCR<sub>1A</sub>*** et **mise à un** sur ***BOTTOM***.

- En mode inversé, la sortie est **à un** sur égalité et **raz** sur ***BOTTOM***.

- Du fait de son fonctionnement en simple pente, on va 2 fois plus vite.

Figure 3.5: Le mode *PWM* rapide

**Fréquence** Dans ce mode la fréquence est définie par :

$$f_{OC1A\text{ PWM}} = \frac{f_{clkI/O}}{N \cdot (1 + TOP)}$$

$N$  représente le facteur de prédivision (1,8,64,256,1024)

**Valeurs particulières** Attention à ne pas changer la valeur  $TOP$  avec une valeur inférieure à la valeur courante de celle du comparateur. De plus, pour une valeur  $TOP = 0$  on aura un quasi front à chaque top d'horloge.

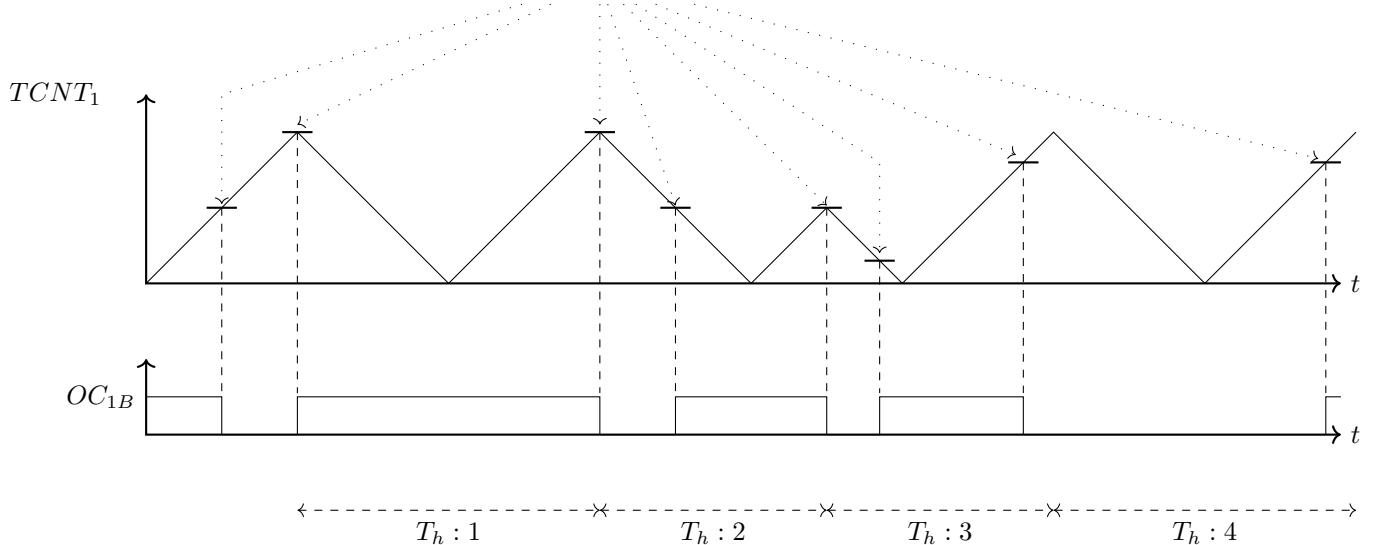

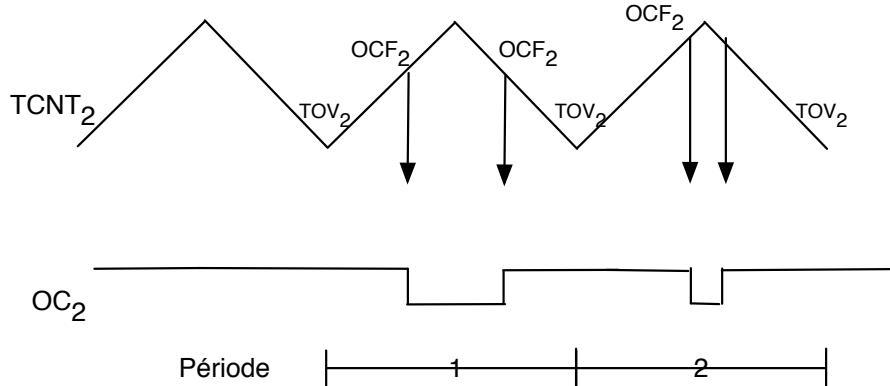

d) Le mode *PWM* à phase correcte  $WGM1_{3:0}=1,2,3,10$  ou 11

Ce mode permet d'obtenir une haute résolution de *PWM* à phase correcte. On est cette fois ci sur du double pente avec comparaison de seuil. Le compteur compte de la valeur *BOTTOM* à *TOP* puis il décrémente jusqu'à *BOTTOM* et recommence indéfiniment.

**Instant de commutation de  $OC1_x$**  Cette commutation dépend du registre  $OCR_{1x}$  et de la valeur  $TOP$ . On voit ces instants de commutation dans la figure 3.2.3 où deux événements se produisent lors des montées et des descentes :

- En mode non inversé,  $OC1_x$  est **raz** sur l'égalité de  $TCNT_1$  avec  $OCR_{1x}$  en comptant, et **mis à un** sur l'égalité de  $TCNT_1$  avec  $OCR_{1x}$  en décomptant.

- En mode inversé,  $OC1_x$  est **mis à un** sur l'égalité de  $TCNT_1$  avec  $OCR_{1x}$  en comptant, et **raz** sur l'égalité de  $TCNT_1$  avec  $OCR_{1x}$  en décomptant.

**Remarque 3.2.3**  $OCR_{1x}$  sont mis à jour sur  $TOP$ . Cela signifie que si  $OCR_{1x}$  est modifié pendant une pente, sa nouvelle valeur n'est prise en compte que sur le prochain  $TOP$

Ce mode à double pente à une fréquence de hachage maximale évidemment deux fois plus petite que celle à simple pente, mais son caractère symétrique le rend plus utilisé dans les applications de commande de moteurs.

**Résolution** La résolution varie de la valeur 2 bits à 16 bits, elle dépend de la valeur de  $OCR_{1A}$  ou  $ICR_1$ . La résolution de la *PWM* est donnée par l'équation :

$$R_{PCPWM} = \frac{\log(TOP + 1)}{\log(2)}$$

Dans ce mode le compteur est incrémenté jusqu'à ce que la valeur atteigne soit une des valeurs : 0x00FF, 0x01FF, 0x03FF ( $WGM1_{3:0} = 1, 2$ , ou 3), soit la valeur dans  $ICR_1$  ( $WGM1_{3:0} = 10$ ), soit la valeur dans  $OCR_{1A}$  ( $WGM1_{3:0} = 11$ ).

Dès que  $TCNT_1$  a alors atteint  $TOP$  alors  $OC1A$  commute et  $TCNT_1$  décompte dès lors.

### Égalité de comparaison avec $OCR_{1B}$

**Attention** Là encore, lorsque l'on change la valeur  $TOP$  on doit s'assurer qu'elle est supérieure à la valeur courante de  $TCNT_1$

**Fréquence** Dans ce mode la fréquence est définie par :

$$f_{OC_{1A}PCPWM} = \frac{f_{clk_{I/O}}}{2.N.(1 + TOP)}$$

$N$  représente le facteur de prédivision (1,8,64,256,1024)

**Mode inversé ou non** En positionnant les bits  $COM1x1 : 0$  à 2 on aura du non inversé. En positionnant les bits  $COM1x1 : 0$  à 3 on aura de l'inversé

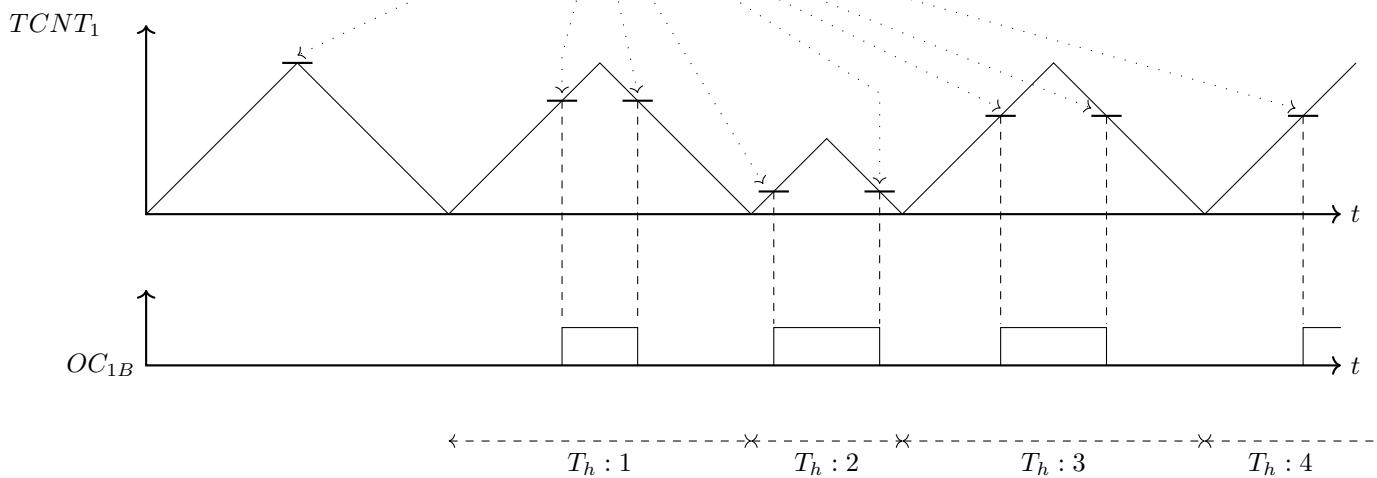

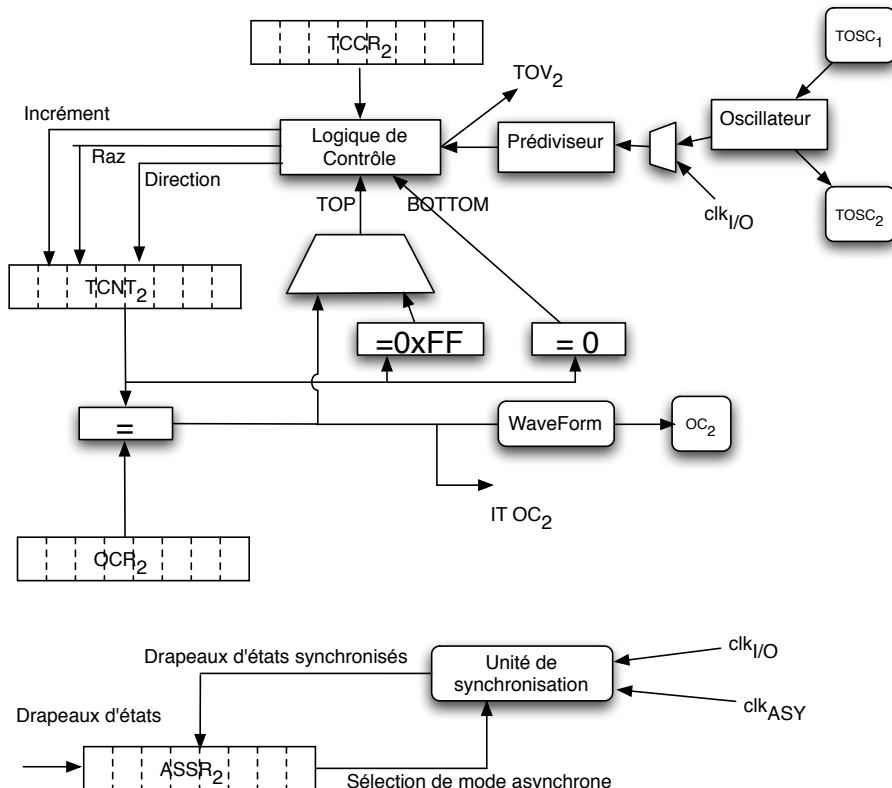

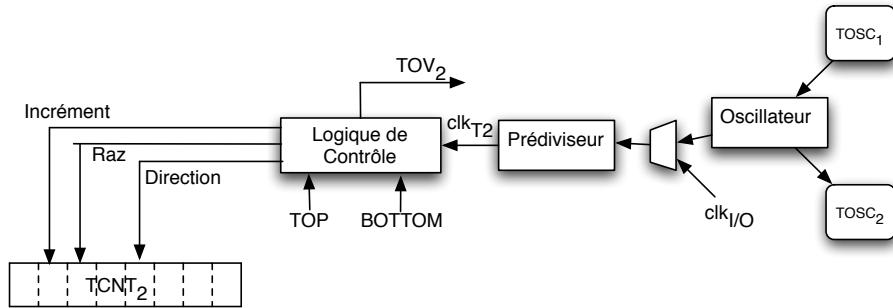

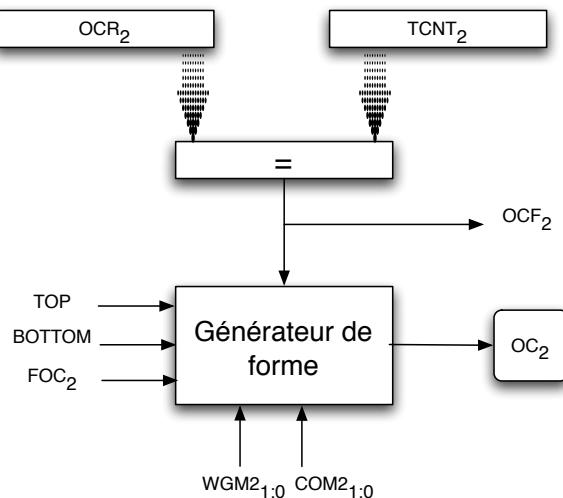

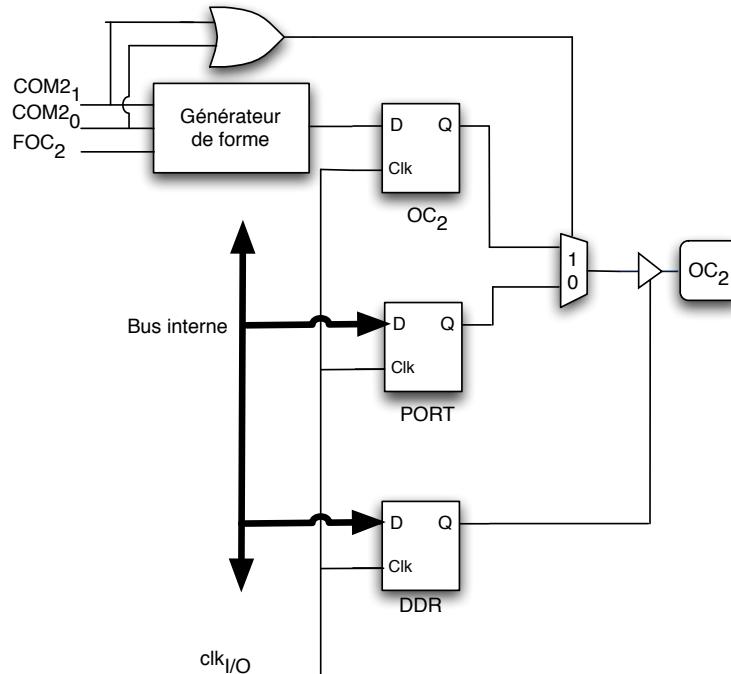

e) Le mode  $PWM$  à phase et fréquence correcte : "MLI Centrée"  $WGM1_{3:0} = 8$  ou  $9$