# CARTES ELECTRONIQUES

## Cours N°4 :

Chap. 5 – CONTRÔLES

Chap. 6 – METHODES ET OUTILS

D'ANALYSE / AMELIORATION

Chap. 7 – COÛTS

# CARTES ELECTRONIQUES

- 1 - INTRODUCTION

- 2 - CIRCUIT IMPRIME NU

- 3 - COMPOSANTS ET INSERTION

- 4 - BRASAGE / ASSEMBLAGES

- ⇒ 5 - CONTRÔLES

- ⇒ 6 - METHODES ET OUTILS D'ANALYSE / AMELIORATION

- ⇒ 7 - COÛTS

# CONTRÔLES

1 - OBJECTIFS

2 - TYPES DE CONTRÔLE

2.1 - Inspection

2.2 - Tests électriques

2.3 - Déverminage/vieillissement

# 1 - OBJECTIFS

Pourquoi tester ? ↳ limiter les éléments H.S chez le client

- ① Image de marque chez le client (fiabilité des produits et délais maîtrisés)

- ② Coûts des réparations sur les retours clients

- ③ Coût de production (coût produit final selon la rapidité de correction dans le process)

Règle du facteur 10 :

Test du composant

Test fonctionnel carte

Test d'ensemble du produit

Dépannage sur site

⇒ *Où et quand tester ?*

⇒ *Impact des composants ?*

## *2.1 – Inspection (sans contact à la carte)*

### 2.1.1 Types de défauts sur cartes câblées

### 2.1.2 Système automatique d'inspection optique : AOI

### 2.1.3 Contrôle par Rayons X

## 2.1.1 - Types de défauts sur cartes câblées

*Composant H.S.*

*Erreur de composant*

*Composant absent*

*Composant mal orienté*

*Soudure ouverte*

*Court-circuit*

*Mauvaise soudure*

*Défaut fonctionnel*

☞ Exemples critères d'acceptation et de refus

☞ Photos défauts

☞ Contrôle visuel : mise en œuvre et limitation

➤ Les classes en électronique selon les IPC

## 2.1.2 - Dispositif de contrôle optique

Système Automatique d'Inspection Optique : AOI

*Défaut visible par AOI*

➡ Document

# AOI

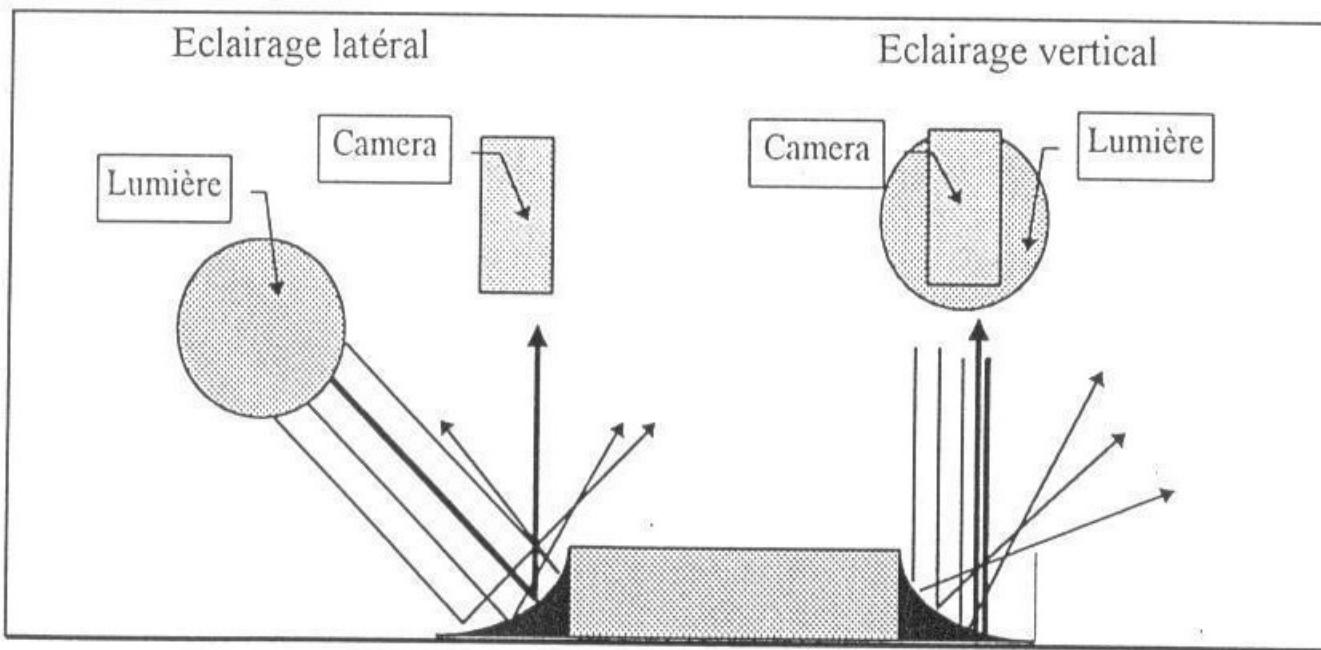

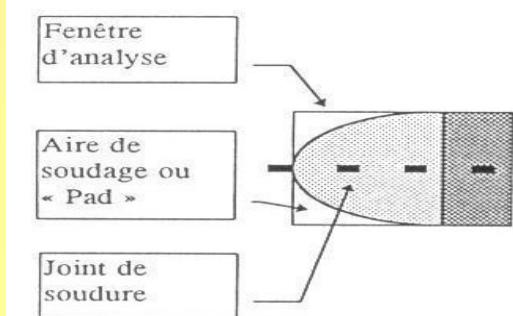

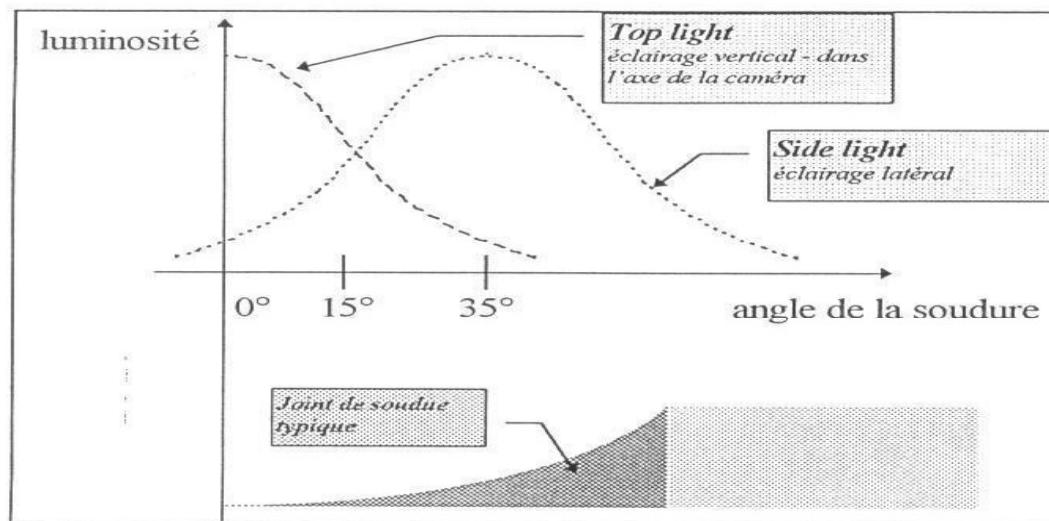

Le contrôle visuel des joints de soudure nécessite d'appréhender le relief. Pour visualiser les reliefs, il faut soit deux angles de visualisations soit deux angles d'éclairage: deux sources de lumière : une source latérale et une source verticale ( dans l'axe de la caméra ).

# AOI

Plus la pente de la soudure est importante et plus la lumière réfléchie depuis la source latérale vers la caméra est importante.

Et inversement, plus cette pente est faible et plus la lumière réfléchie depuis la source verticale vers la caméra sera importante.

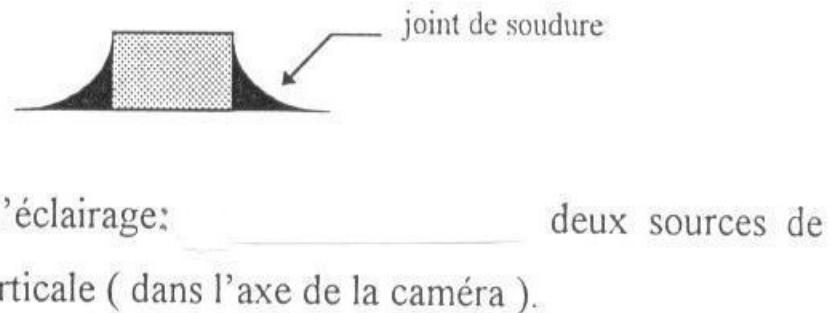

Le diagnostique est alors le suivant:

Si le résultat est positif en un point donné de l'image alors cela signifie qu'il existe en ce point un relief (la pente est supérieure à 15°).

Si le résultat est négatif alors il n'y a pas de relief, le joint est plat en ce point.

Si on trace l'amplitude de la luminosité apparente de la soudure suivant les deux sources de lumière, on obtient le graphe suivant:

Pour pouvoir comparer facilement les deux images (éclairage vertical & éclairage latéral),

on réalise la soustraction de ces deux images. (Latérale - verticale).

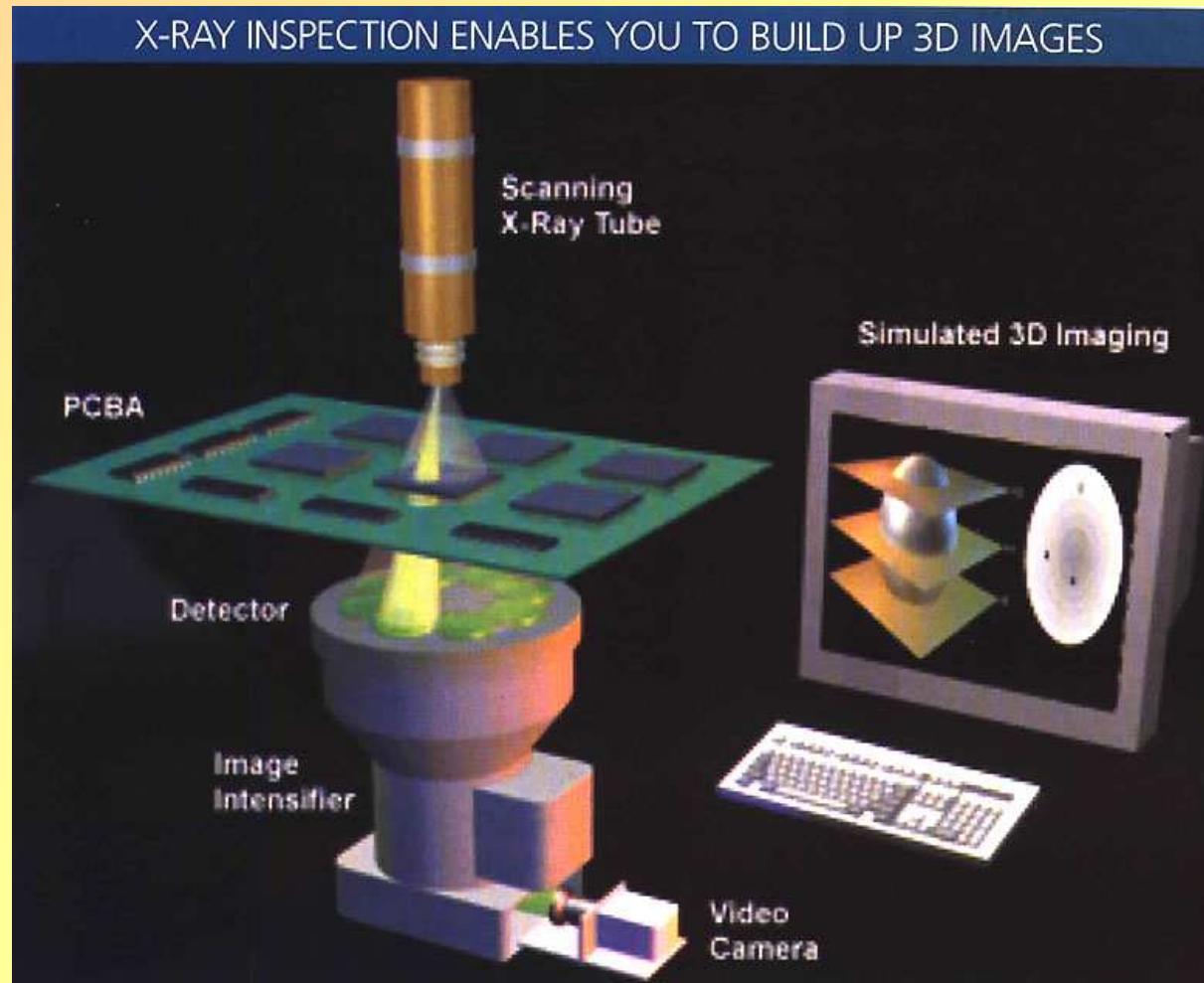

### 2.1.3 - Contrôle par Rayons X

Document

11

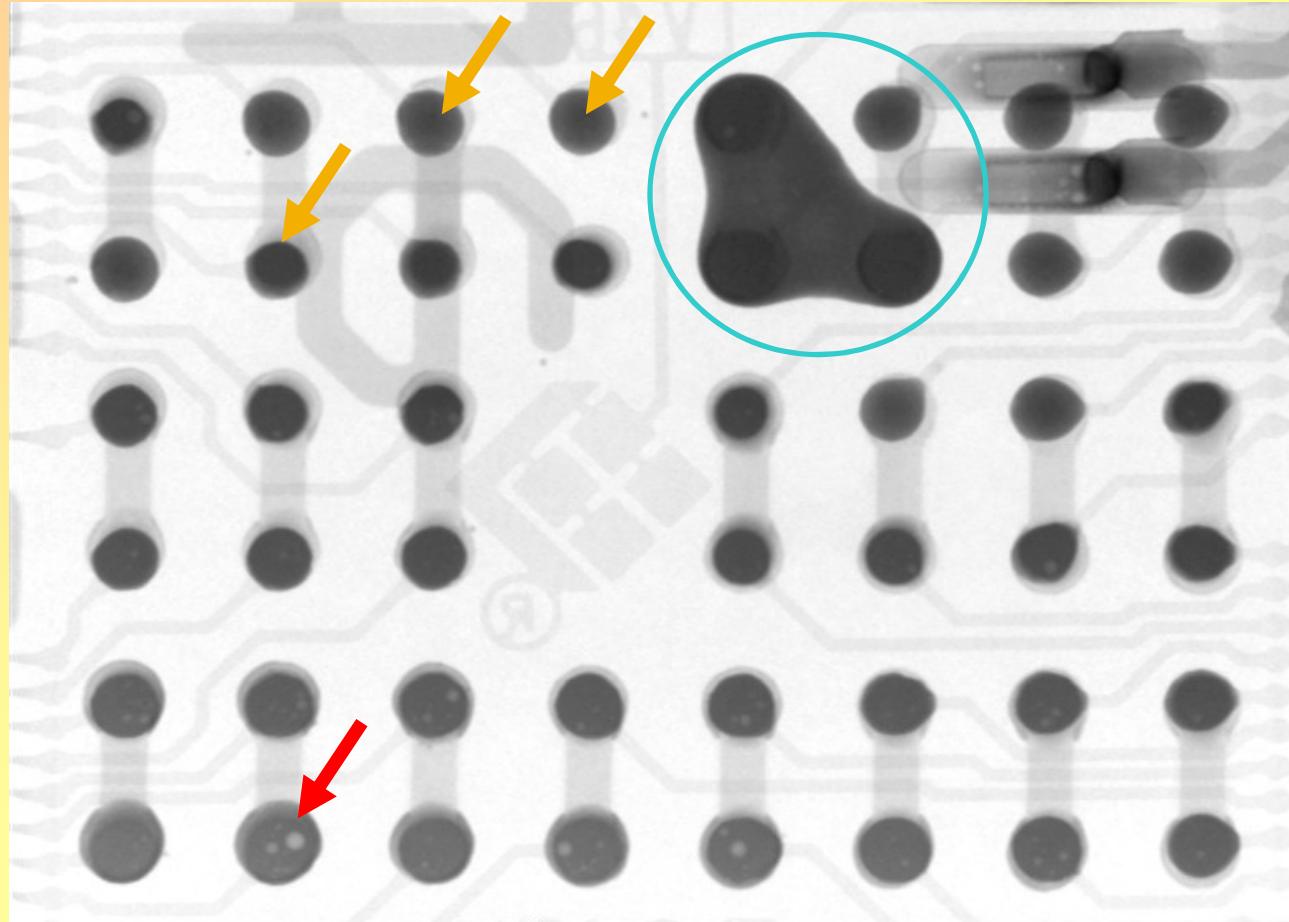

RX : Joints de soudure type BGA

80 - 130 kV 10 - 30  $\mu$  A Vue directe

► Défauts détectables en vue directe: **bulles d'air**, joints manquants, **courts-circuits**, variations en diamètre et rondeur, **joints ouverts**.

⇒ Règles de contrôle des BGA

⇒ PV contrôle BGA

12

⇒ Photos

⇒ Film

⇒ Fiche

Technique

machine RX

## 2.2 – Tests électriques

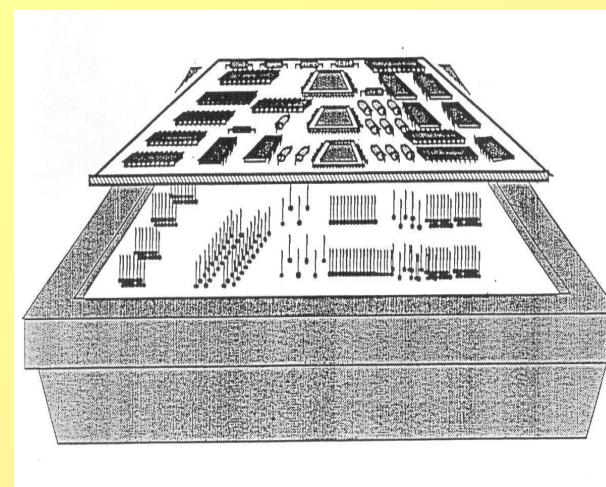

### 2.2.1 *In situ [ou in circuit](avec contact à la carte)*

Principe : Tester chaque composant de la carte

à l'endroit où il est implanté en inhibant son

environnement électronique

2.2.1.1 - à lits de clous

2.2.1.2 - sous pointes mobiles

### 2.2.2 *Fonctionnel*

Principe : Vérifier le fonctionnement de la carte

## 2.2.1 - Contrôle in-situ

### OBJECTIF :

Vérifier, après toutes les opérations d'assemblage de la carte, sa parfaite conformité par rapport à son dossier de définition.

**PRINCIPE GENERAL :** Comme son nom l'indique, cette méthode consiste à tester chaque composant de la carte à l'endroit où il est implanté en ignorant son environnement.

Le test est obtenu en « déplaçant » un instrument de mesure aux bornes de chaque composant.

Le contrôle in-situ nécessite donc un accès direct aux bornes de chaque composant ou plus précisément, à chaque équipotentielle.

Cet accès est obtenu au moyen d'un interface qui assure le lien entre le testeur universel et la carte à contrôler.

# Contrôle in-situ

**TEST ANALOGIQUE :** Sont testés les courts-circuits, les continuités, les composants passifs (R, L, C ...), les composants actifs analogiques ( Diodes, Transistors, Ampli OP ...)

Les ressources sont des générateurs de tension, de courant, des mesureurs de tension, de courant.

**TEST NUMERIQUE :** Est testée la table de vérité de chaque composant digital

**AVANTAGES :**

- Investissement initial (le testeur) relativement peu coûteux.

- Écriture du programme de test facilement automatisable (C.A.O.)

- Diagnostique rapide et sans ambiguïté.

- Tous les défauts d'une carte sont détectés en un seul passage.

- Détection des défauts « non fonctionnels » susceptibles d'altérer la fiabilité de la carte.

**INCONVENIENTS :**

- Nécessite un interface spécifique à chaque produit

- Ne peut être mis en place que pour un produit stabilisé lié aux difficultés de modification de l'interface.

- Est de plus en plus confronté à l'inaccessibilité des équipotentielles.

[Document](#)

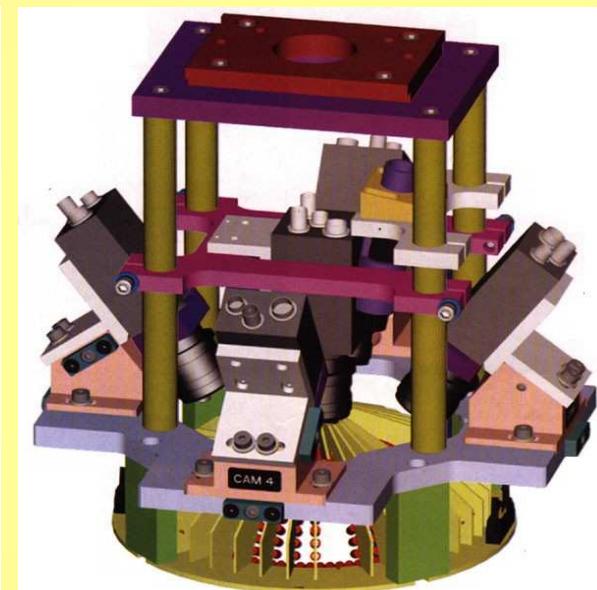

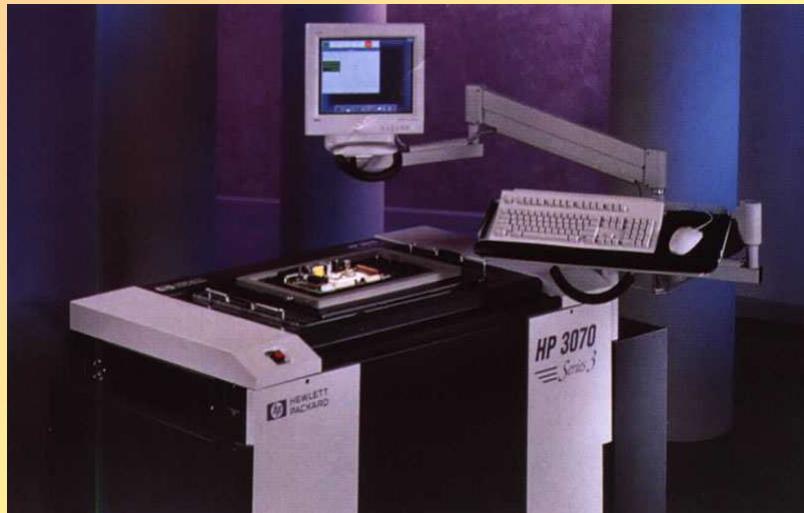

## Exemples de Testeurs multi-pointes

### 2.2.1.1 - Test in-situ multi-pointes

lit de clous

Interface de test in-situ à lit de clous

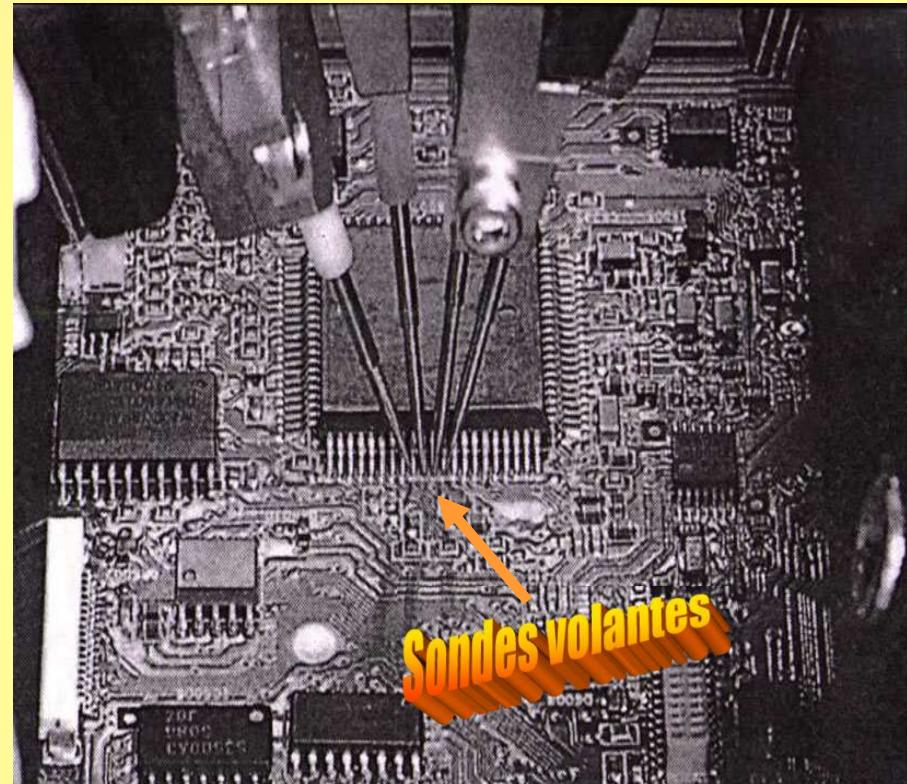

## 2.2.1.2 - Testeur *in-situ* sous pointes mobiles (flying probes)

Exemple de

Testeur sous

pointes mobiles

## L'accessibilité à quoi ?

POINTS de TEST => Place

- Plage de Test

- déportée

- sur l'équipotentielle  $\phi 0.85 \text{ mm}$  (0.7 mm mini)

- Via

- Plage d'accueil du composant CMS

- Queue de composant traversant

Si possible

Tous les points

sur la même face

Si non (ex : TAKAYA)

Pour un composant donné, les

points doivent être sur la même face

# Les moyens de ces accès ?

## PALPEURS

Testeur à

Pointes Mobiles

- nombre de palpeurs limité ( 4+2 )

- pointe fine supportée par la tête mobile

- résolution  $\sim 50 \mu\text{m}$

- pression programmable

Testeur à

lit à clous

- nombre maximal fonction du testeur

- choix possible de la tête du palpeur

- palpeur enfoncé dans une embase

- embase insérée dans un plateau

Pas inter-palpeurs = 2.54 mm

(exceptionnellement 1.27 mm)<sup>19</sup>

=> Types de clous

# Synthèse

Efficacité comparative des tests in situ :

|                                  | Temps d'accès | Qualité de mesure | Haute densité | Coût Outillage |

|----------------------------------|---------------|-------------------|---------------|----------------|

| <b>Testeur à lit à clous</b>     | A             | A                 | D             | D              |

| <b>Testeur à Pointes Mobiles</b> | D             | A                 | B             | A              |

A = Très bon

B = Bon

C = Mauvais

D = Très mauvais

## 2.2.2 - Contrôle fonctionnel

OBJECTIF : Vérifier le bon fonctionnement de la carte électronique.

PRINCIPE GENERAL : La carte électronique est considérée comme une entité dont les seuls accès sont les connecteurs d'entrée et de sortie. Sont donc vérifier les fonctions de transfert telles que :

$$\{ S \} = \int \{ E \}$$

TEST ANALOGIQUE : Sont testés les consommations, gains, bandes passantes asservissements ...

Les ressources sont des appareils de mesure programmables (BUS IEEE-488). Ces appareils peuvent se présenter sous forme d'éléments indépendants ou de cartes intégrées dans le testeur (V.X.I.)

# Contrôle fonctionnel

TEST NUMERIQUE : La ressource matérielle est un canal numérique par point de test comprenant un « driver » pour commander un niveau logique et un « sensor » pour mesurer un niveau logique.

Les ressources logicielles sont pour les entrées, un ensemble de « stimuli » par fonction de transfert à tester appelé « vecteurs de tests » et des analyseurs de signature logiciels pour les sorties.

L'écriture des programmes de test fait appel à des logiciels de simulation. Il existe deux types de programmation pour ces testeurs :

- les tests BON/MAUVAIS

- les tests avec diagnostic

TEST BON/MAUVAIS : L'objectif est de trier les cartes bonnes et mauvaises fonctionnellement et de vérifier le bon fonctionnement de ces dernières après réparation.

Une méthode consiste en l'utilisation de logiciels dits « auto-test » réalisé par le concepteur du produit.

L'autre utilise un ATPG ( Automatique Test Programm Generator). Il s'agit de logiciels qui génèrent automatiquement les vecteurs de test et analysent les signatures correspondantes. Ces logiciels sont issus des simulateurs de fonctionnement.

# Contrôle fonctionnel

## TEST DIAGNOSTIC :

L'objectif est de tester le bon fonctionnement de la carte et si elle est en faute, de trouver le composant qui est à l'origine de cette faute .

La méthodologie conduit à constituer une base de données appelée « bibliothèque de fautes » qui sera utilisée par une sonde guidée pour remonter la fonction de transfert jusqu'au composant en cause. Cette bibliothèque de fautes est élaborée en faisant appel à des logiciels de simulation de fautes.

## AVANTAGES :

Permettre la vérification du bon fonctionnement de la carte à vitesse réelle.

Ne nécessite pas d'interface spécifique onéreux.

Intervention possible dès la conception de la carte, sans attendre d'avoir une carte physique.

N'est pas tributaire des modifications de la carte.

## INCONVENIENTS :

Entraîne un investissement initial important.

L'écriture et la mise au point des programmes de test nécessitent des outils logiciels complexes et onéreux.

On ne détecte qu'un seul défaut par passage.

# Conclusion sur les tests électriques et inspection

## Efficacité des différentes méthodes de test

|               |                           | API                        | HUM             | AOI                          | AXI                       | FLY          | ICT                  | FCT         |

|---------------|---------------------------|----------------------------|-----------------|------------------------------|---------------------------|--------------|----------------------|-------------|

|               |                           | Automated paste inspection | Contrôle visuel | Automated optical inspection | Automated Xray inspection | flying probe | In-situ multipointes | Fonctionnel |

| Bad part      | Composant mauvais         | ■                          | ■               | ■                            | ■                         | ■            | ■                    | ■           |

| Wrong part    | Erreur de composant       | ■                          | ■               | ■                            | ■                         | ■            | ■                    | ■           |

| BGA solder    | Mauvaise soudure sous BGA | ■                          | ■               | ■                            | ■                         | ■            | ■                    | ■           |

| Solder Open   | Soudure ouverte           | ■                          | ■               | ■                            | ■                         | ■            | ■                    | ■           |

| Solder Short  | Court-circuit             | ■                          | ■               | ■                            | ■                         | ■            | ■                    | ■           |

| Missing       | Composant absent          | ■                          | ■               | ■                            | ■                         | ■            | ■                    | ■           |

| Misoriented   | Composant mal orienté     | ■                          | ■               | ■                            | ■                         | ■            | ■                    | ■           |

| Insuff/Excess | Trop ou trop peu de pâte  | ■                          | ■               | ■                            | ■                         | ■            | ■                    | ■           |

| Functional    | Défauts fonctionnels      | ■                          | ■               | ■                            | ■                         | ■            | ■                    | ■           |

|               |                           |                            |                 |                              |                           |              |                      |             |

|               | Couverture < 25 %         | ■                          |                 |                              |                           |              |                      |             |

|               | 25% < < 95 %              |                            | ■               |                              |                           |              |                      |             |

|               | Couverture > 95 %         |                            | ■               |                              |                           |              |                      |             |

⇒ Répartition des défauts

⇒ Exemple de stratégie de test

⇒ Processus de contrôle

⇒ Ligne automatique cartes électroniques

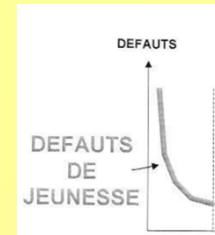

## 2.3 – Déverminage

But ? ↗ Mettre en évidence les défauts de jeunesse

Plusieurs moyens :

- ① En température stable et fonctionnement

- BURN IN : Statique ou dynamique

- ② En vibration

- ③ En températures variables et hors tension

- VLT / VRT / Chocs thermiques

- ④ ...

↗ Processus de production

↗ Equipements Industriels

↗ Ligne assemblage

# CHAPITRE 6

## METHODES ET OUTILS D'ANALYSE / AMELIORATION

1 - DIAGRAMME CAUSES / EFFET

2 - ANALYSE DE PARETO

3 - LE S.P.C. OU M.S.P.

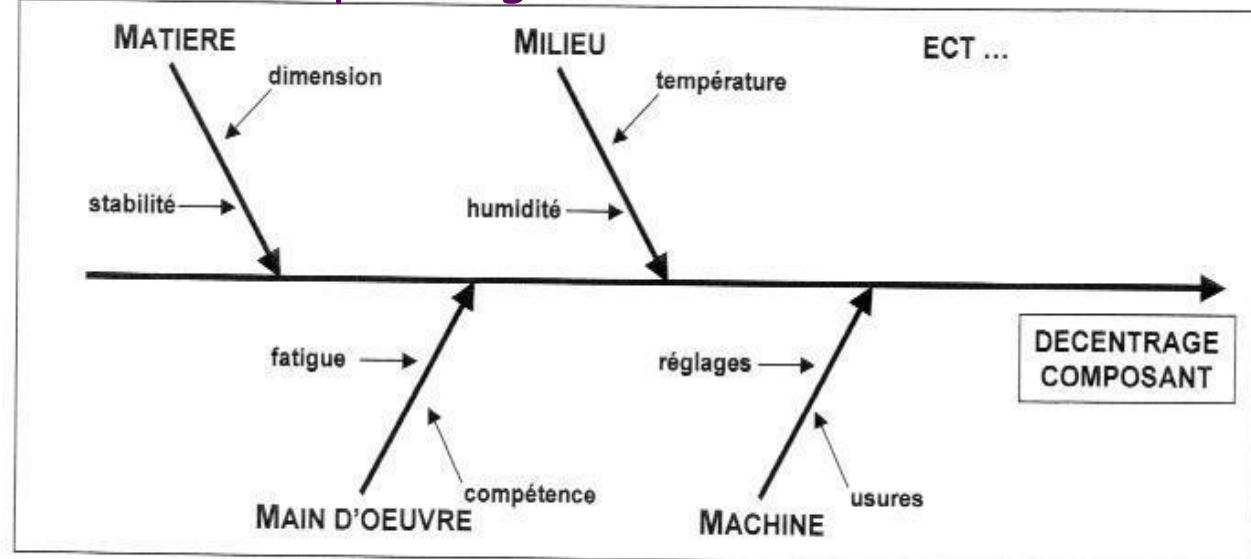

# 1 – DIAGRAMME CAUSES/EFFET - « ISHIKAWA » - ARÊTE DE POISSON

But : classer toutes les causes d'un effet par familles et sous-familles.

Exemple : les « 5 M » : Matière; Machine, Méthode, Milieu et Main-d'œuvre sont les 5 catégories les plus utilisées dans les DCE de l'industrie.

Exemple Diagramme Causes-Effet

Chaque cause est évaluée et si possible éliminée ou réduite

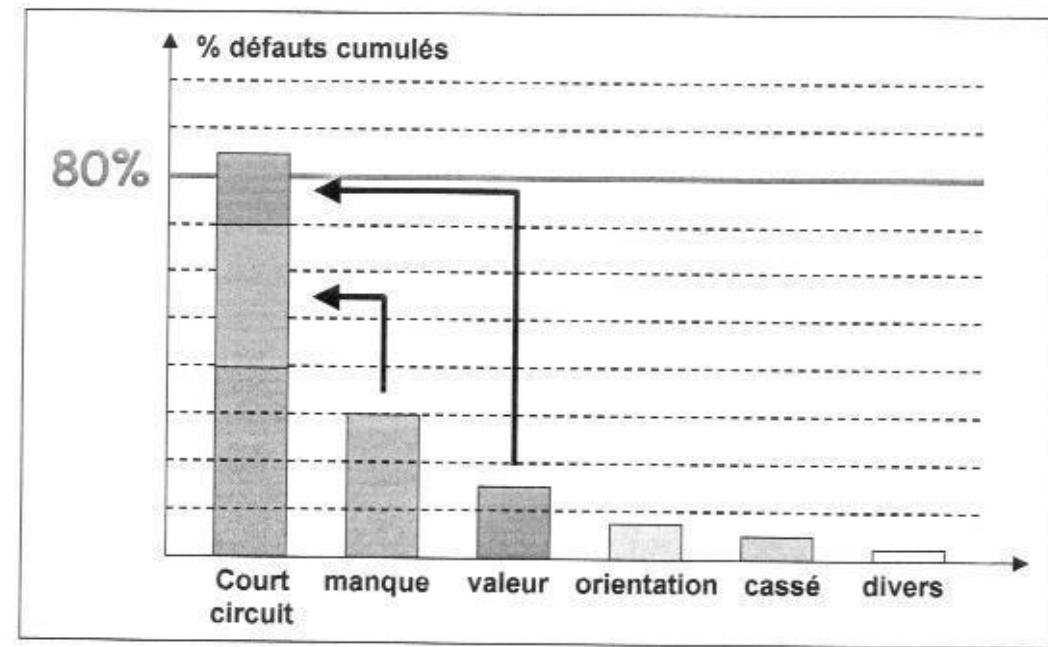

## 2 – ANALYSE ET DIAGRAMME DE PARETO

But : déterminer l'importance relative de problèmes pour les classer par ordre décroissant d'importance.

Histogramme en colonnes représentatif de ce classement pour mettre en valeur les priorités d'améliorations.

La loi du 80/20 dit que 80% d'un défaut provient de 20 % des causes.

Exemple Diagramme de PARETO

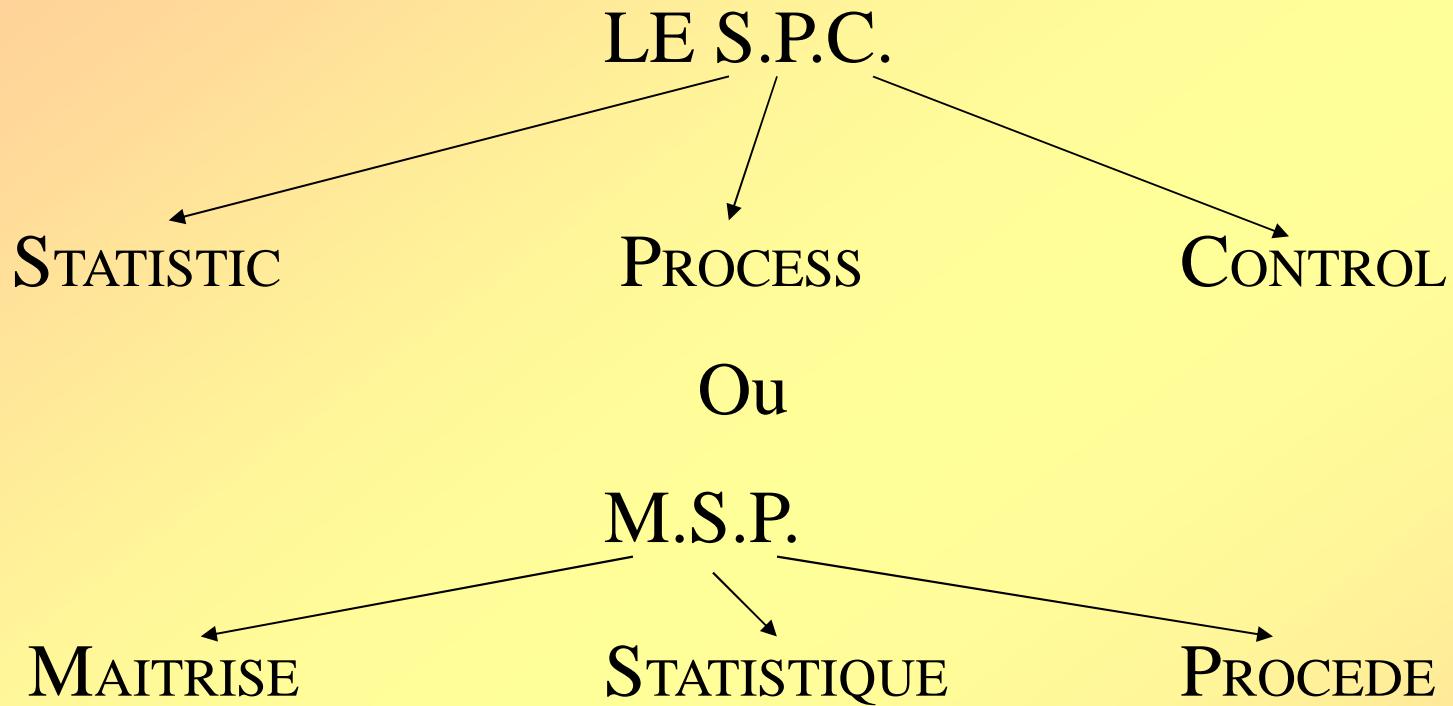

### 3 – Le S.P.C.

But : permettre la maîtrise, par l'opérateur à son poste, du process qu'il pilote.

Basé sur les lois statistiques (loi normale essentiellement) : outil puissant en production moyenne et grande série.

Production => Renseignement sur la performance =>

Possibilité 1 : Intervenir sur le procédé = amélioration du futur

Possibilité 2 : Intervenir sur la produit = réparation du passé

### ↳ Document

Par principe, le procédé est parfaitement défini,

- Tolérances matières,

- Fatigue de l'opérateur, ou autre opérateur,

- Fluctuations de  $T^\circ$ ,

- Usure de l'outil de la machine,

- Appréciation de l'opérateur réalisant la mesure.

**MAIS**

Il n'existe pas deux procédés aux caractéristiques rigoureusement identiques.

Ces différences s'appellent **VARIATIONS**.

Alors => améliorer le procédé consiste à éliminer le plus possible les causes de variations.

SPC : l'outil principal de ce suivi réactif en temps réel est la **carte de contrôle**, feuille d'enregistrement détectant en préventif et en temps réel les dérives qualité, et permettant de fabriquer à zéro défaut sous contrôle.

**UTILITES** : implication, réduction des rebuts, maîtrise du procédé, gains.

# CHAPITRE 7

## COÛTS

- COÛTS DE PRODUCTION

- COÛTS DE DEVELOPPEMENT

- COÛTS DE COMMERCIALISATION

- COÛTS QUALITE

Prix de vente

Prix de revient

Coûts de production

Coûts de développement

Coûts de commercialisation

Impôts

Marge nette

Prix de vente

Prix de revient

Coûts de production

Coûts directs matière

Prix d'achat

Coûts du test d'entrée

Coûts du stockage

Coûts directs main d'œuvre

Charges de structure

Coûts de développement

Coûts de commercialisation

Impôts

Marge nette

Prix de vente

Prix de revient

**Coûts de production**

Coûts directs matière

**Coûts directs main d'œuvre**

Salaires bruts

Charges sociales

Congés payés, prime,..

Absentéisme

Formation, délégations,..

Charges de structure

Coûts de développement

Coûts de commercialisation

Impôts

**Marge nette**

## Prix de revient

### Coûts de production

Coûts directs matière

Coûts directs main d'œuvre

### Charges de structure

Coût du personnel indirect

encadrement

ordonnancement

Coûts machine

amortissement

exploitation (maintenance, consommation)

Coûts bâtiment (location, amortissement, entretien)

Impôts et taxes (taxe professionnelle)

Services généraux (informatiques, eau, électricité, télécoms)

Services extérieurs

Coûts de développement

Coûts de commercialisation

Prix de vente

Prix de revient

Coûts de production

Coûts de développement

Main d'œuvre

Amortissement des outils matériels et logiciels

Coûts de commercialisation

Main d'œuvre

Frais de voyage

Frais de publicité

Impôts

Marge nette

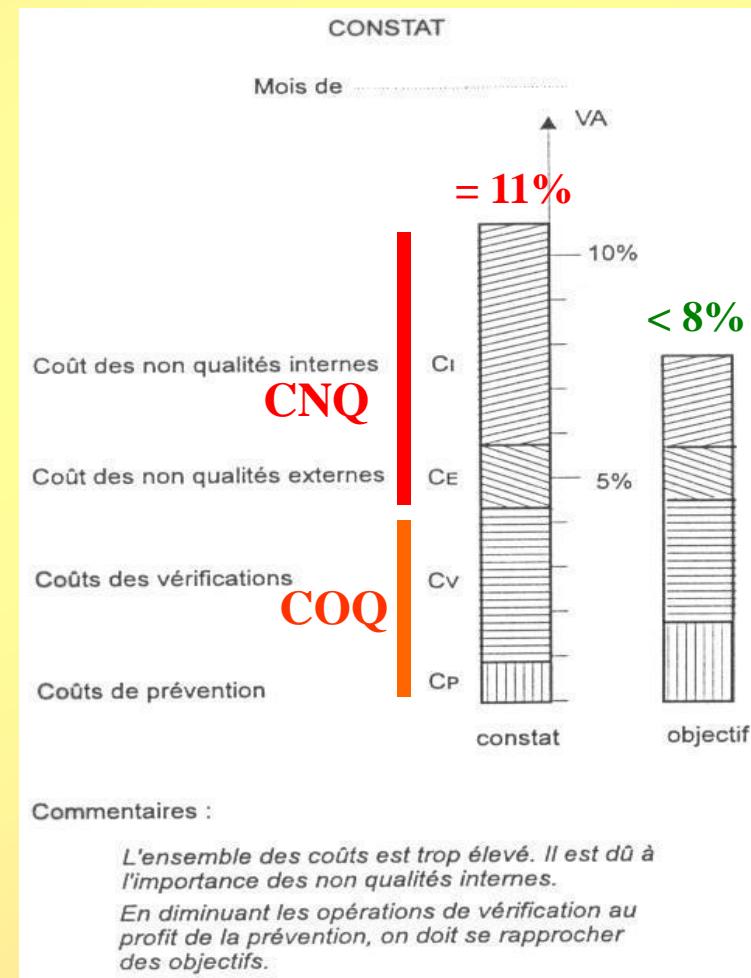

# COÛTS QUALITÉ

## 1) COUTS DES ANOMALIES INTERNES (Ci) :

- LES REBUTS DE FABRICATION

- LES RETOUCHES EN FABRICATION

- LES ERREURS D'APPROVISIONNEMENT

- LES ARRETS TECHNIQUES DE PRODUCTION

## 2) COUTS DES ANOMALIES EXTERNES (Ce)

## 3) COUTS DE PREVENTION (C<sub>P</sub>)

## 4) COUTS DE DETECTION OU DE VERIFICATION (C<sub>V</sub>)

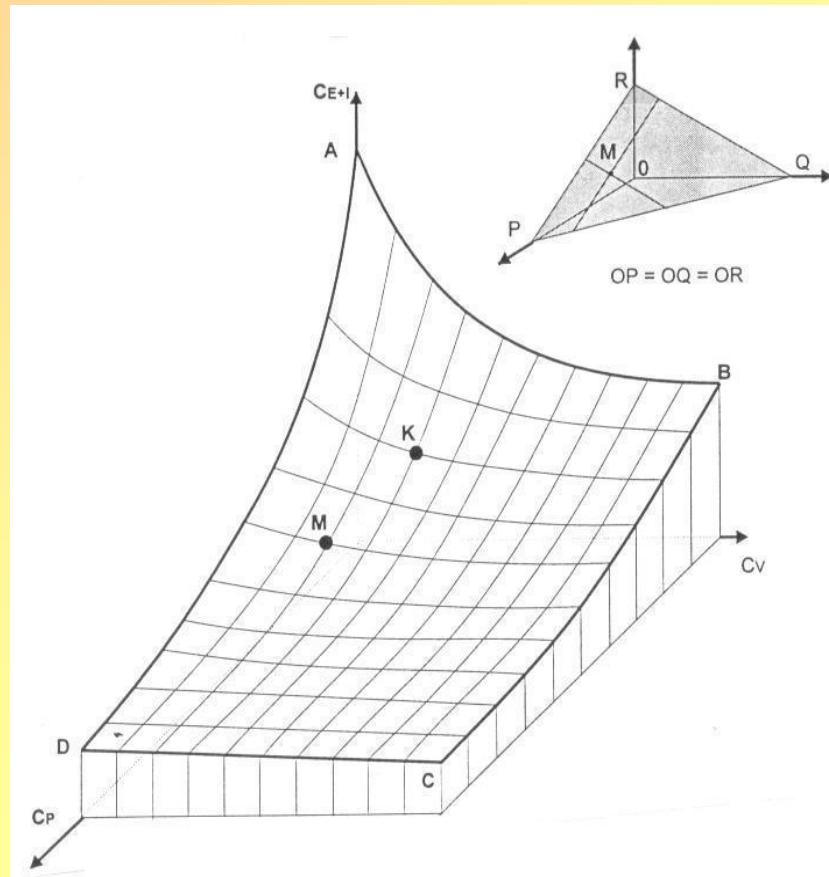

## 5) RELATION ENTRE LES DIVERS COUTS

**CNQ** Coûts de non-qualité

**COQ** Coûts d'obtention de la qualité

$$CQ = CNQ + COQ$$

# Coûts qualité

Un prévisionnel, de réduction des CQ, représenté par l'histogramme empilé des CQ, est un garant de la pérennité de la stratégie qualité.